#### **Durham E-Theses**

# Investigation of Low-temperature Solution-processed Thin-Film Transistors for Flexible Displays

JEONG, YESUL

#### How to cite:

JEONG, YESUL (2016) Investigation of Low-temperature Solution-processed Thin-Film Transistors for Flexible Displays, Durham theses, Durham University. Available at Durham E-Theses Online: http://etheses.dur.ac.uk/11507/

#### Use policy

The full-text may be used and/or reproduced, and given to third parties in any format or medium, without prior permission or charge, for personal research or study, educational, or not-for-profit purposes provided that:

- a full bibliographic reference is made to the original source

- a link is made to the metadata record in Durham E-Theses

- the full-text is not changed in any way

The full-text must not be sold in any format or medium without the formal permission of the copyright holders.

Please consult the full Durham E-Theses policy for further details.

# Investigation of Low-temperature Solution-processed Thin-Film Transistors for Flexible Displays

by

Yesul Jeong

**Ustinov College**

A thesis presented for the degree of

Doctor of Philosophy

Centre for Molecular and Nanoscale Electronics

School of Engineering and Computing Sciences

**Durham University**

February 2016

## **Abstract**

This thesis describes the electrical behaviour of solution-processed zinc oxide thin film transistors (ZnO TFTs) fabricated at low temperature. First, the electrical properties of solution-processed ZnO films are reported. Spin-coated ZnO films annealed at 150 °C exhibit significant sensitivity to the ambient environment. However, their stability can be improved by hydrogen plasma treatment. Zinc oxide TFTs (channel width/length =  $4000/200 \mu m$ ) fabricated by chemical spray pyrolysis at the low process temperature of 140 °C are investigated. The resulting transistors exhibit a saturation mobility of 2 cm<sup>2</sup>/Vs measured in air; this value is reduced to 0.5 cm<sup>2</sup>/Vs under vacuum. The effect of hydrogen plasma treatment on spin-coated ZnO TFTs is then studied. The electrical characteristics of untreated TFTs exhibit large hysteresis and a positive threshold voltage shift on repeated measurements. These effects are reduced by the hydrogen plasma and an increase in carrier mobility is observed. In a further investigation, a solution-processed silicon dioxide gate insulator for application in the TFTs is used; a perhydropolysilazane (PHPS) precursor is spin-coated with subsequent thermal treatment to form the SiO<sub>2</sub> layer. Exposure to oxygen plasma leads to an acceleration of the conversion reaction, resulting in good insulating properties (leakage current density of ~10<sup>-7</sup> A/cm<sup>2</sup>) and TFT performance (channel width/length = 1000/50 µm, carrier mobility of 3.2 cm<sup>2</sup>/Vs, an on/off ratio of ~10<sup>7</sup>, a threshold voltage of -1.3 V and a subthreshold swing of 0.2 V/decade). Finally, a photolithographic process is introduced for the fabrication of 'short' channel solution-processed ZnO TFTs. Optimum processing conditions are established and used for the fabrication of transistors having various channel dimensions. Devices with a minimum channel length of 5 µm possessed a mobility of 1.5 x 10<sup>-2</sup> cm<sup>2</sup>/Vs, on/off ratio of 10<sup>6</sup> and good contact between the S/D electrodes and the semiconductor. The relatively low mobility could originate from gate insulator roughness caused by the photolithographic processes.

# **Contents**

| Abstract                                                        | i      |

|-----------------------------------------------------------------|--------|

| List of Figures                                                 | V      |

| List of Tables                                                  | xi     |

| Declaration                                                     | xii    |

| Copyright                                                       | xii    |

| Acknowledgements                                                | xiv    |

| Chapter 1 Introduction                                          | 1      |

| References                                                      | 6      |

| Chapter 2 Thin Film Transistors                                 | 8      |

| 2.1 Operation of TFTs                                           | 8      |

| 2.2 Vacuum-processed TFTs                                       | 15     |

| 2.3 Solution-processed TFTs                                     | 20     |

| 2.4 Conclusions                                                 | 27     |

| References                                                      | 28     |

| Chapter 3 Experimental Techniques                               | 35     |

| 3.1 Introduction                                                | 35     |

| 3.2 Experimental Methods                                        | 35     |

| 3.3 Conclusions                                                 | 58     |

| References                                                      | 59     |

| Chapter 4 Electrical Conduction Mechanisms in Solution-processe | ed ZnO |

| Films                                                           | 60     |

| 4.1 Introduction                                                | 60     |

| 4.2 Conductivity of Solution-processed ZnO Films                | 60     |

| 4.3 Solution-processed ZnO Films with Hydrogen Plasma Treatment | 69     |

| 4.4 Conclusions                                                 | 77     |

| References                                                                      | 78  |

|---------------------------------------------------------------------------------|-----|

| Chapter 5 ZnO TFTs Fabricated by Chemical Spray Pyrolysis                       | 81  |

| 5.1 Introduction                                                                | 81  |

| 5.2 Fabrication of ZnO Thin Film by Spray Pyrolysis                             | 81  |

| 5.3 Spray-coated ZnO TFTs                                                       | 85  |

| 5.4 Environmental Effects                                                       | 91  |

| 5.5 Transistors with a Polymer Gate Dielectric                                  | 95  |

| 5.6 Conclusions                                                                 | 98  |

| References                                                                      | 99  |

| Chapter 6 Effect of Hydrogen Plasma Treatment on ZnO TFTs                       | 101 |

| 6.1 Introduction                                                                | 101 |

| 6.2 Device Characteristics                                                      | 102 |

| 6.3 Modelling                                                                   | 114 |

| 6.4 Conclusions                                                                 | 116 |

| References                                                                      | 117 |

| Chapter 7 ZnO TFTs with a Solution-processed Gate Insulator                     | 118 |

| 7.1 Introduction                                                                | 118 |

| 7.2 Solution-processed Polymer Dielectric                                       | 119 |

| 7.3 Solution-processed Silicon Oxide Dielectric                                 | 122 |

| 7.4 PHPS Gate Insulator with Plasma Treatment                                   | 130 |

| 7.5 Conclusions                                                                 | 149 |

| References                                                                      | 151 |

| Chapter 8 Short Channel Solution-processed ZnO TFTs                             | 154 |

| 8.1 Introduction                                                                | 154 |

| 8.2 Short Channel ZnO TFT with a Thermally Grown SiO <sub>2</sub> Insulator     | 155 |

| 8.3 Short Channel ZnO TFT with a Solution-processed SiO <sub>2</sub> Insulator. | 162 |

| 8.4 Conclusions                                                                 | 171 |

| References                                             | 172 |

|--------------------------------------------------------|-----|

| Chapter 9 Conclusions and Suggestions for Further Work | 174 |

| 9.1 Conclusions                                        | 174 |

| 9.2 Suggestions for Further work                       | 176 |

| Publications                                           | 180 |

# **List of Figures**

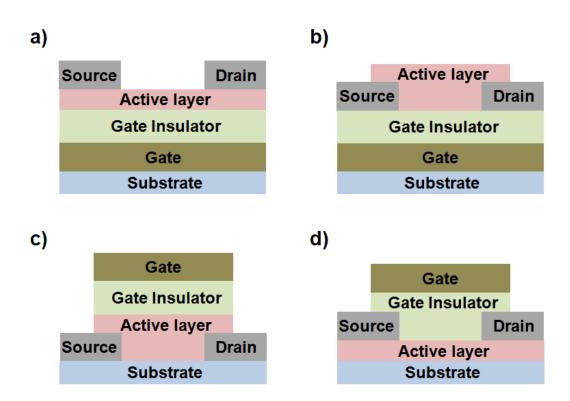

| Figure. 2.1. Four possible TFT structures: (a) bottom gate, top contact, (b) bottom gate, bottom contact, (c) top gate, bottom contact, and (d) top gate, top contact 9                                                                                                                               |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

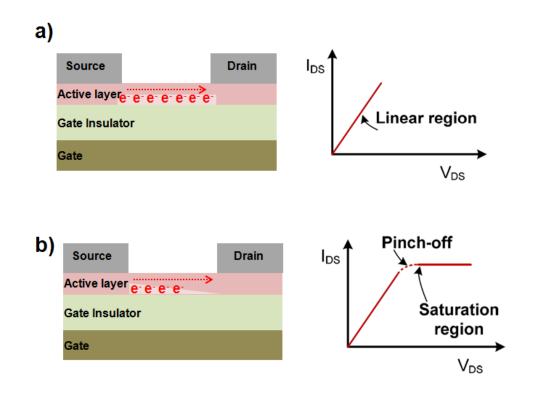

| Figure. 2.2. Ideal n-type TFT operation: (a) linear region, and (b) saturation region.                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                       |

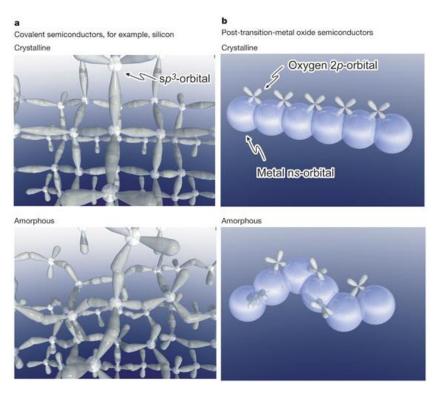

| Figure. 2.3. Comparison of atomic orbital overlap in crystalline and amorphous semiconductors for (a) silicon and (b) metal oxide semiconductor. <sup>2,3</sup>                                                                                                                                       |

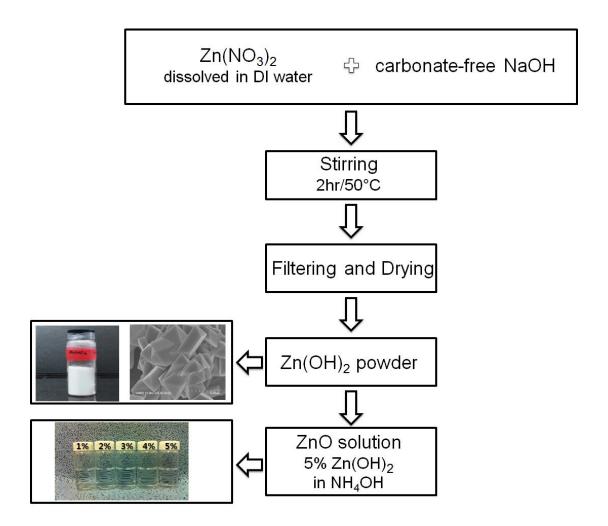

| Figure. 3.1. Synthesis procedure of ZnO solution based on zinc hydroxide 37                                                                                                                                                                                                                           |

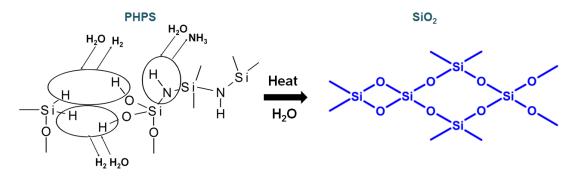

| Figure. 3.2. Conversion of PHPS into SiO <sub>2</sub> in a high humidity environment 38                                                                                                                                                                                                               |

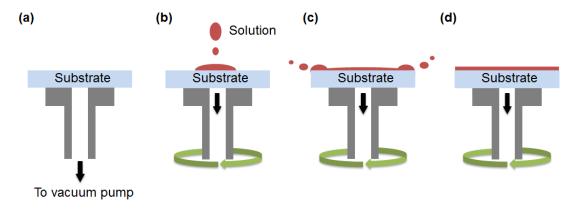

| Figure. 3.3. Schematic diagram of spin coating: (a) placing the sample on the vacuum chuck, (b) dispensing the solution onto the substrate, (c) spinning at a low speed and (d) coating the solution uniformly on the substrate by spinning at a relatively high speed                                |

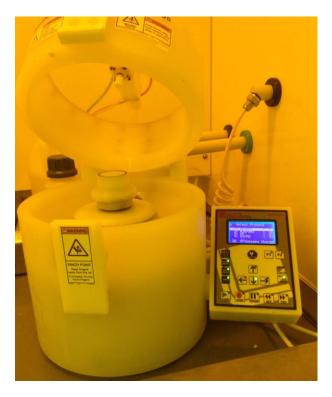

| Figure. 3.4. Photograph of WS-650 Spin coater                                                                                                                                                                                                                                                         |

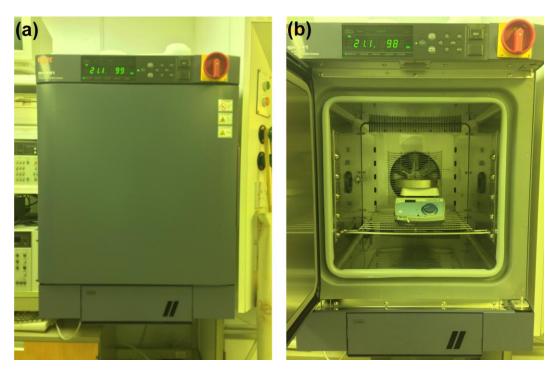

| Figure. 3.5. (a) Espec SH-641 bench-top type temperature and humidity chamber and (b) hotplate placed inside the chamber                                                                                                                                                                              |

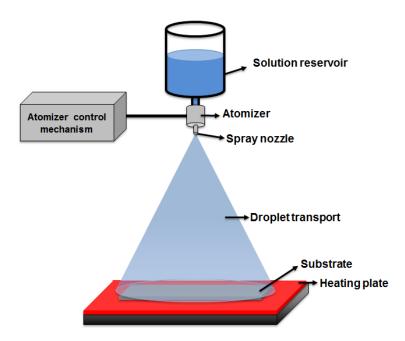

| Figure. 3.6. Schematic diagram of a spray pyrolysis system. <sup>8</sup>                                                                                                                                                                                                                              |

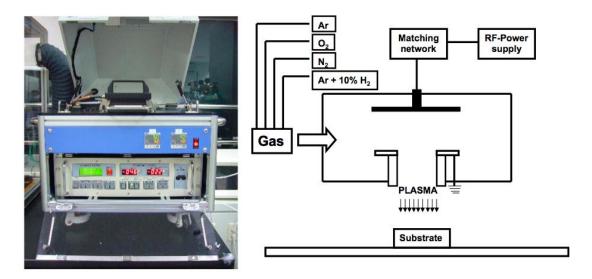

| Figure. 3.7. Photograph and schematic diagram of FemtoScience AP 100 colar plasma system                                                                                                                                                                                                              |

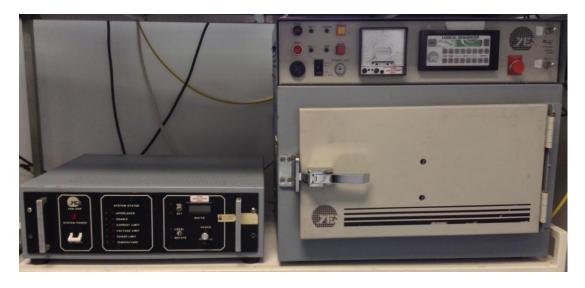

| Figure. 3.8. YES-R3 oxygen plasma etching system                                                                                                                                                                                                                                                      |

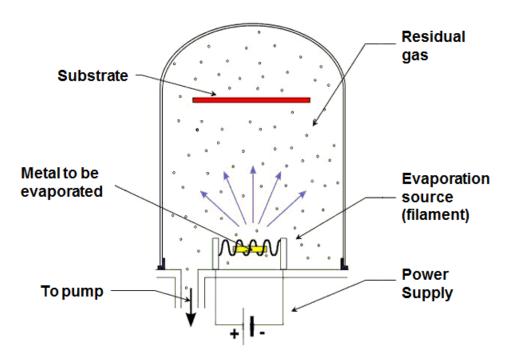

| Figure. 3.9. Schematic diagram of a thermal evaporator                                                                                                                                                                                                                                                |

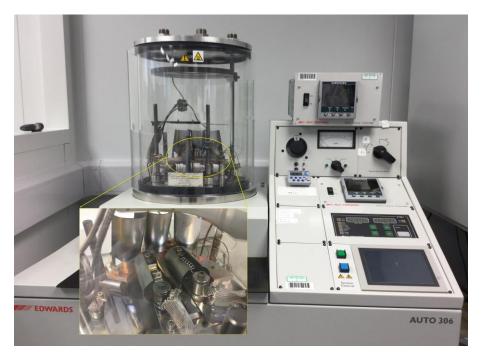

| Figure. 3.10. Photograph of an Edwards Auto 306 evaporator                                                                                                                                                                                                                                            |

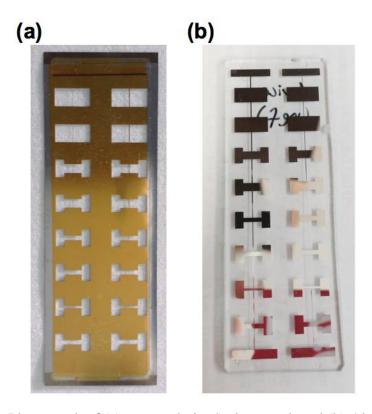

| Figure. 3.11. Photograph of (a) source-drain shadow mask and (b) Al source-drain electrodes deposited using the shadow mask                                                                                                                                                                           |

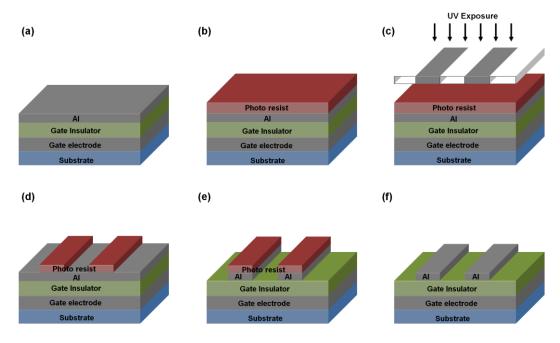

| Figure. 3.12. Illustration of the transistor fabrication processes using photolithography (a) deposition of the Al electrode, (b) photoresist coating, (c) baking at 95 °C for 5 minutes followed by exposure to UV light, (d) develop, (e) Al etching and (f) stripping of the remaining photoresist |

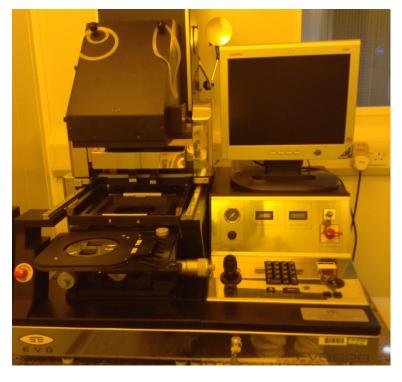

| Figure. 3.13. EVG 620 mask aligning machine                                                                                                                                                                                                                                                           |

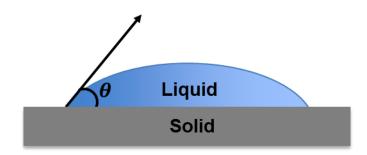

| Figure. 3.14. Schematic diagram of a droplet of water on a solid substrate 51                                                                                                                                                                                                                         |

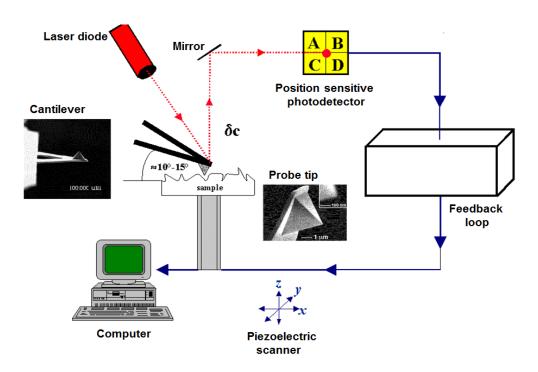

| Figure. 3.15. Schematic diagram of an atomic force microscope                                                                                                                                                                                                                                         |

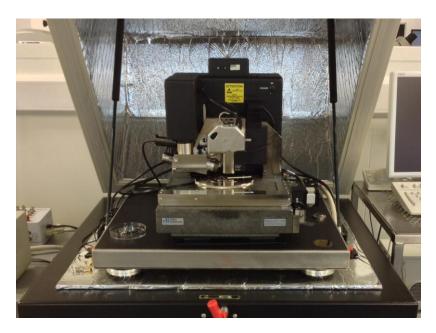

| Figure. 3.16. Digital Instruments Nanoman II AFM                                                                                                                                                                                                                                                      |

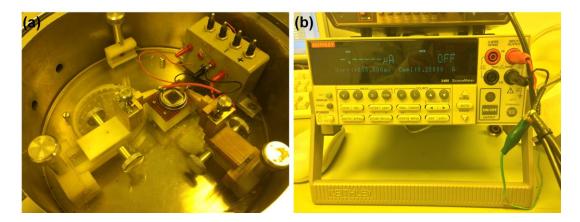

| Figure. 3.17. (a) Two terminal measurement chamber. (b) Keithley 2400                                                                                                                                                                                                                                 |

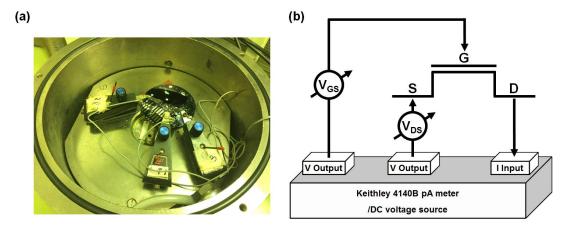

| Figure. 3.18. (a) Three terminal measurement chamber. (b) Circuit diagram of the measurement system                                                                                                                |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

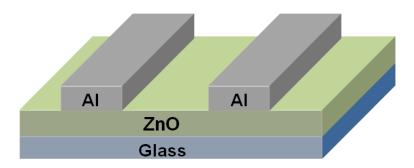

| Figure. 4.1. Schematic diagram of the ZnO/in-plane Al electrodes structure 61                                                                                                                                      |

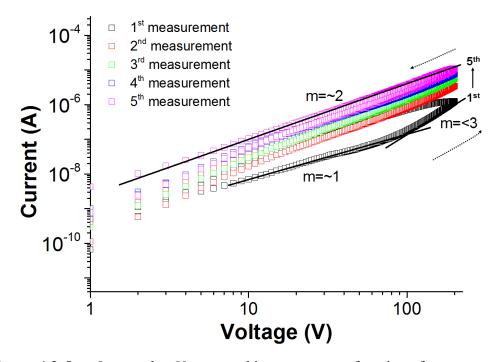

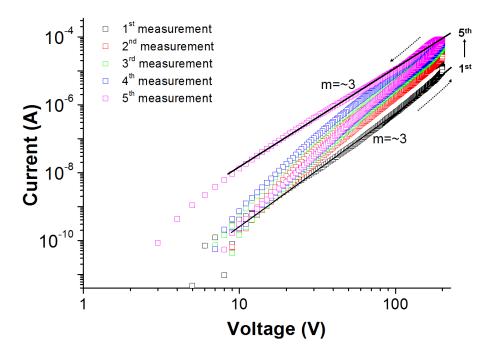

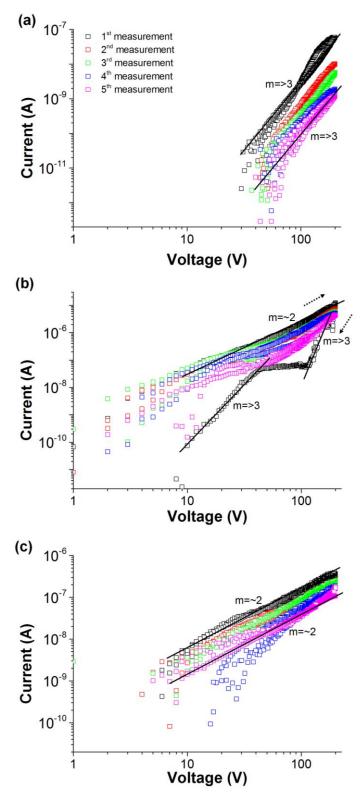

| Figure. 4.2. Log I versus log V measured in vacuum as a function of measurement sequence for a solution-processed ZnO film                                                                                         |

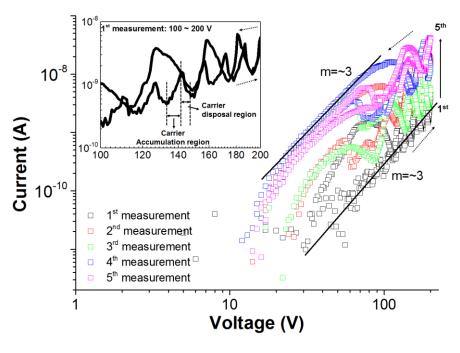

| Figure. 4.3. Log I versus log V measured in oxygen as a function of measurement sequence for a solution-processed ZnO film                                                                                         |

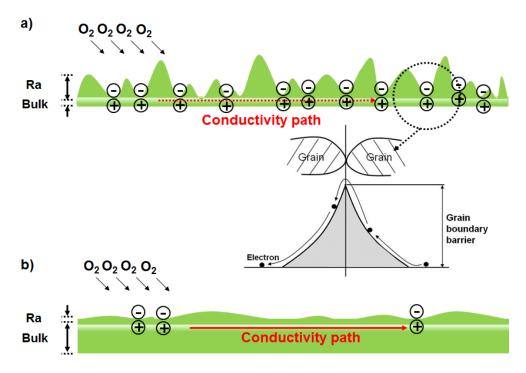

| Figure. 4.4. Schematic diagram of the conductive path through (a) a thin film and (b) a thick film                                                                                                                 |

| Figure. 4.5. Log I versus log V measured in air as a function of measurement sequence for a solution-processed ZnO film                                                                                            |

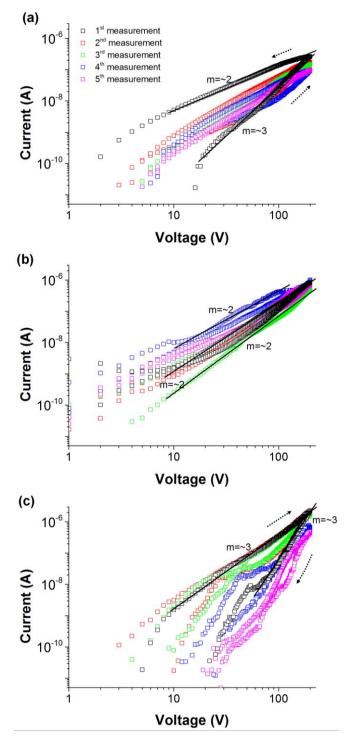

| Figure. 4.6. Log I versus log V for solution-processed ZnO films after hydrogen plasma treatment for (a) 10 min, (b) 15 min and (c) 30 min as a function of measurement sequence in air                            |

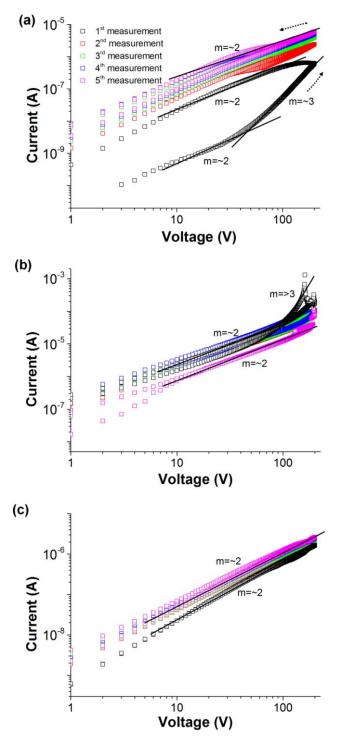

| Figure. 4.7. Log I versus log V for solution-processed ZnO films after hydrogen plasma treatment for (a) 10 min, (b) 15 min and (c) 30 min as a function of measurement sequence in vacuum.                        |

| Figure. 4.8. Log I versus log V for solution-processed ZnO films after hydrogen plasma treatment for (a) 10 min, (b) 15 min and (c) 30 min as a function of measurement sequence in dry oxygen.                    |

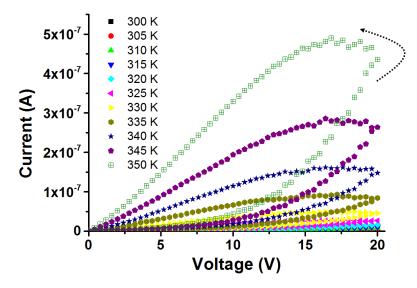

| Figure. 4.9. I versus V characteristics of a solution-processed ZnO film in helium ambient as a function of temperature between 300 K and 350 K                                                                    |

| Figure. 4.10. I versus V characteristics of a solution-processed ZnO film in helium ambient as a function of measurement delay time at a temperature of 350 K75                                                    |

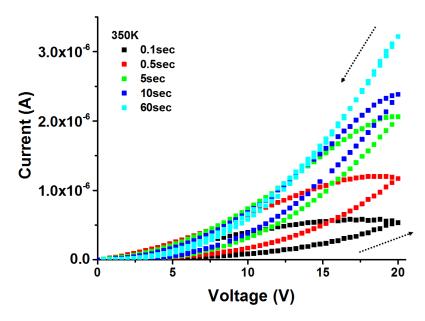

| Figure. 4.11. Current versus temperature properties for ZnO films before and after 15 min of plasma treatment, measured at applied voltages of (a) 0.5 V and (b) 20 V                                              |

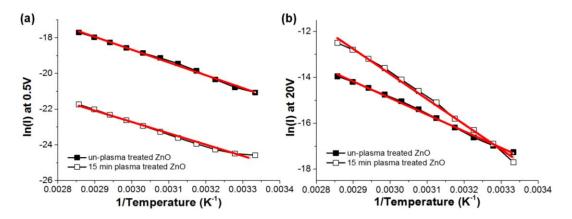

| Figure. 4.12. Ln I versus 1/T characteristics for ZnO films before and after 15min of plasma treatment, measured at applied voltages of (a) 0.5 V and (b) 20 V                                                     |

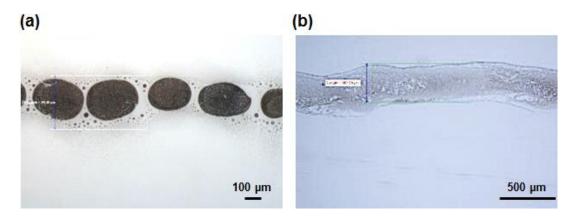

| Figure. 5.1. Optical microscopy images of ZnO sprayed onto (a) Si/SiO <sub>2</sub> and (b) UV ozone plasma treated Si/SiO <sub>2</sub>                                                                             |

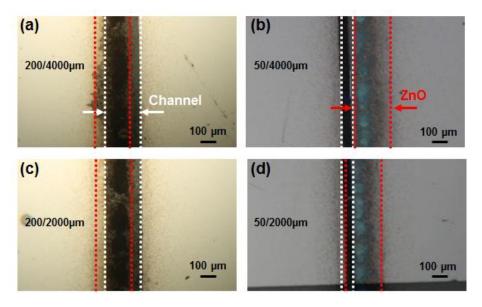

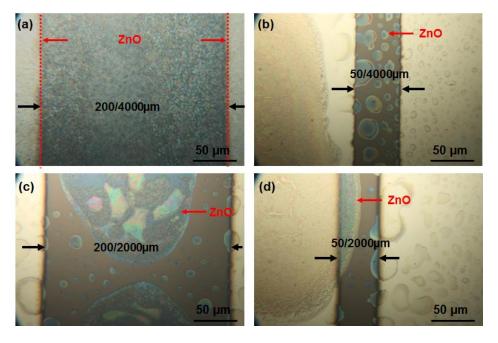

| Figure. 5.2. Optical microscopy images of ZnO sprayed onto linear electrodes with channel length/width of (a) $200/4000~\mu m$ , (b) $50/4000~\mu m$ , (c) $200/2000~\mu m$ and (d) $50/2000~\mu m$ .              |

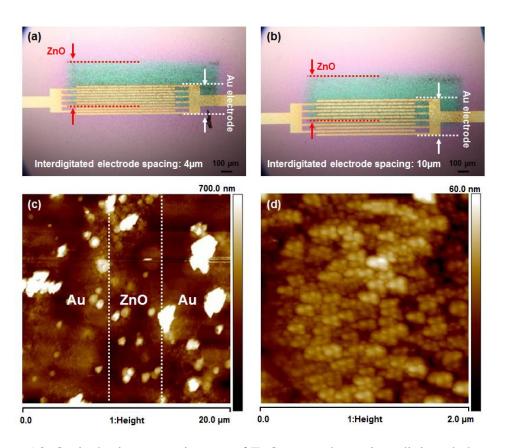

| Figure. 5.3. Optical microscopy images of ZnO sprayed onto interdigitated electrodes with spacing of (a) 4 µm and (b) 10 µm. AFM topography images of spray-coated ZnO at two different magnifications (c) and (d) |

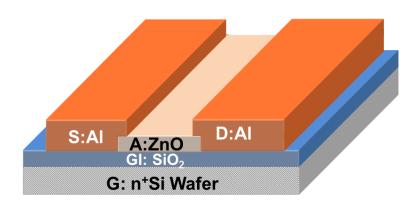

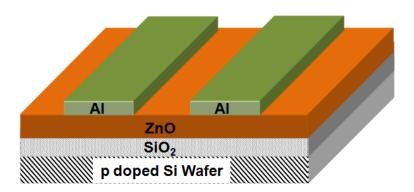

| Figure, 5.4. Schematic diagram of a bottom-gate, top-contact ZnO TFT structure., 86                                                                                                                                |

| Figure. 5.5. Optical microscopy images of ZnO spray-coated onto electrodes with channel length/width of (a) $200/4000~\mu m$ , (b) $50/4000~\mu m$ , (c) $200/2000~\mu m$ and (d) $50/2000~\mu m$                                                                                                                 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure. 5.6. AFM topography image of a ZnO thin film placed between S/D electrodes having length/width of 200/4000 µm                                                                                                                                                                                             |

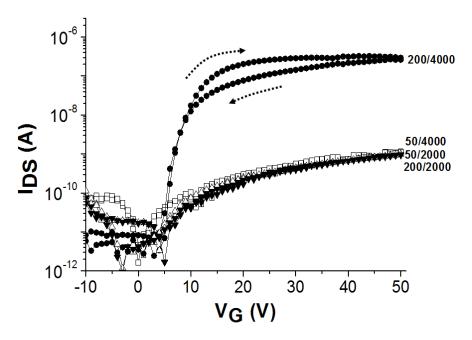

| Figure. 5.7. Transfer characteristics ( $V_{DS}$ =10 V) of spray-coated ZnO TFTs with various channel dimensions.                                                                                                                                                                                                 |

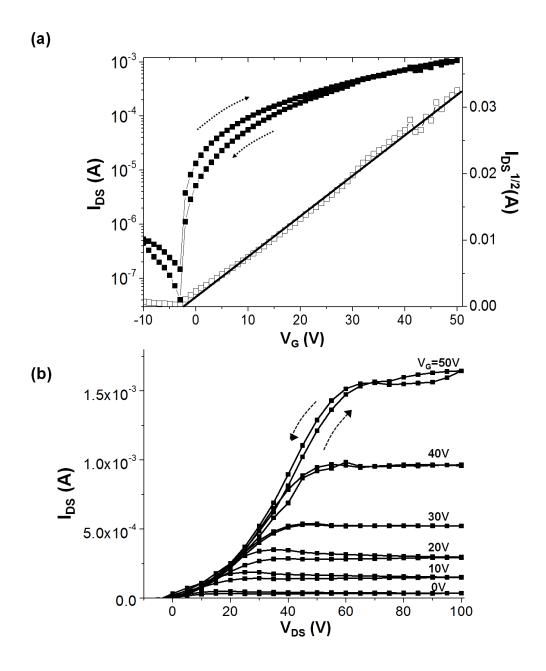

| Figure. 5.8. (a) Transfer characteristics in the saturation region ( $V_{DS}$ =80 V), (b) output characteristics of a top contact ZnO TFT with channel length/width of $200/4000 \ \mu m$ .                                                                                                                       |

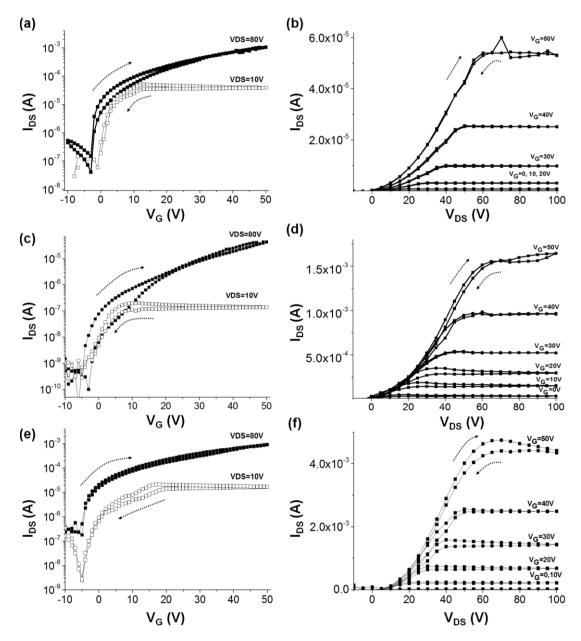

| Figure. 5.9. Transfer and output characteristics, measured in (a,b) air, (c,d) under vacuum for two days, and (e,f) again in air for two days                                                                                                                                                                     |

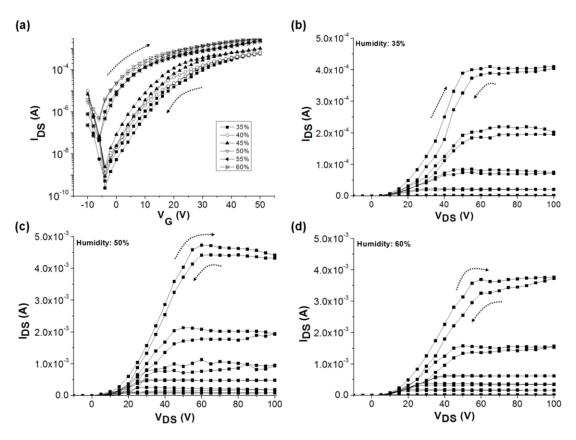

| Figure. 5.10. (a) Transfer in the saturation region ( $V_{DS}$ =80 V) and (b-d) representative output characteristics as a function of the ambient humidity94                                                                                                                                                     |

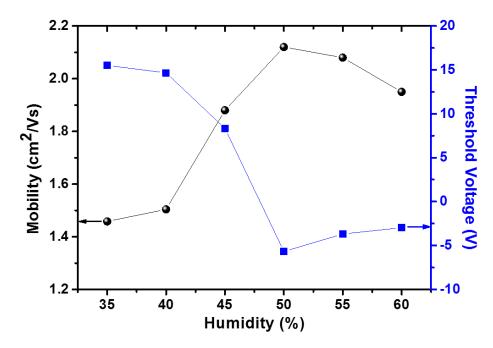

| Figure. 5.11. Carrier mobility and threshold voltage versus humidity for ZnO TFTs measured at room temperature                                                                                                                                                                                                    |

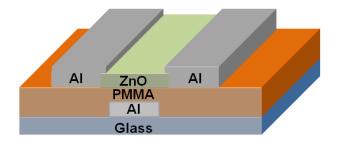

| Figure. 5.12. Schematic diagram of the spray-coated ZnO TFT with PMMA gate dielectric                                                                                                                                                                                                                             |

| Figure. 5.13. Spray-coated ZnO/PMMA TFTs with 0.5 mm/s printing speed. Transfer and output characteristics of devices having channel length/width of (a-b) 50/2000 µm and (c-d) 50/4000 µm                                                                                                                        |

| Figure. 5.14. Spray-coated ZnO/PMMA TFTs with 1.0 mm/s printing speed. Transfer and output characteristics of devices having channel length/width of (a-b) 50/2000 µm and (c-d) 50/4000 µm                                                                                                                        |

| Figure. 5.15. Water contact angle for a PMMA film                                                                                                                                                                                                                                                                 |

| Figure. 6.1. Schematic diagram of the bottom-gate, top-contact ZnO TFT structure.                                                                                                                                                                                                                                 |

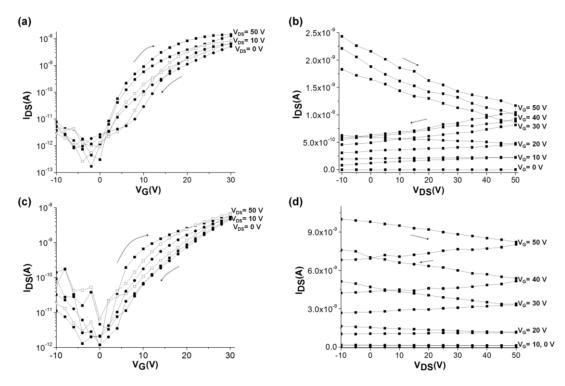

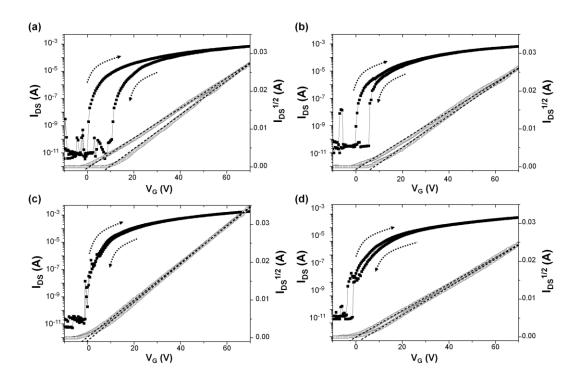

| Figure. 6.2. Transfer characteristics ( $I_{DS}$ vs $V_G$ curve—full symbols) in the saturation region ( $V_{DS}$ =50 V) of (a) reference, (b) 10 min, (c) 15 min, and (d) 30 min plasma treated ZnO TFTs. For each set of data, plots of ( $I_{DS}$ ) <sup>1/2</sup> versus $V_G$ are also shown (open symbols). |

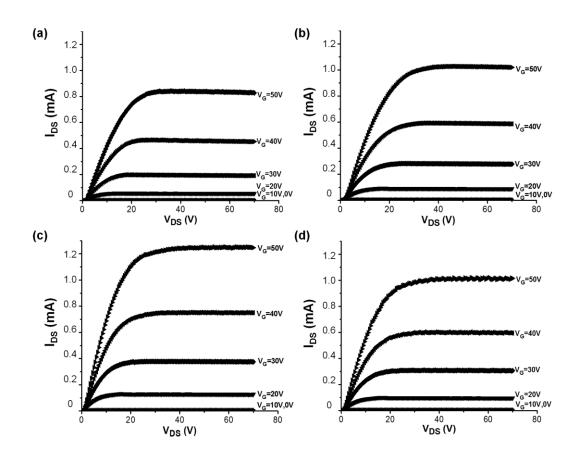

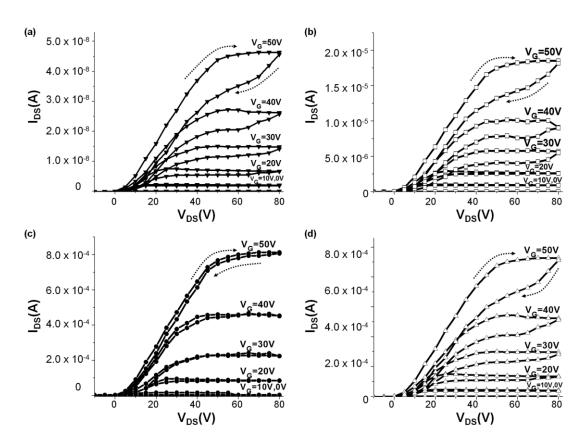

| Figure. 6.3. Output characteristics (I <sub>DS</sub> vs V <sub>DS</sub> curve) of (a) reference, (b) 10 min, (c) 15 min, and (d) 30 min plasma treated ZnO TFTs                                                                                                                                                   |

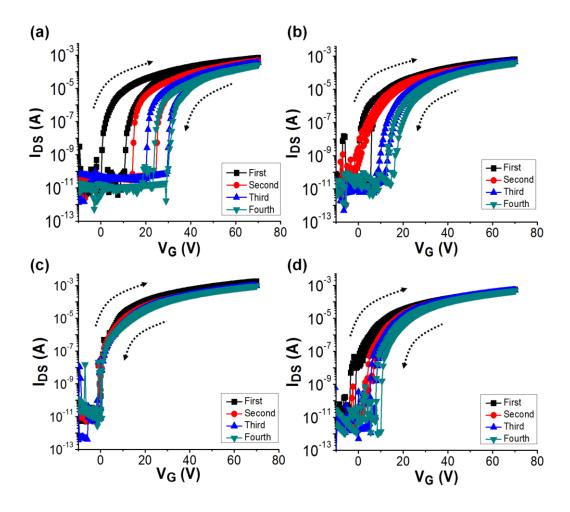

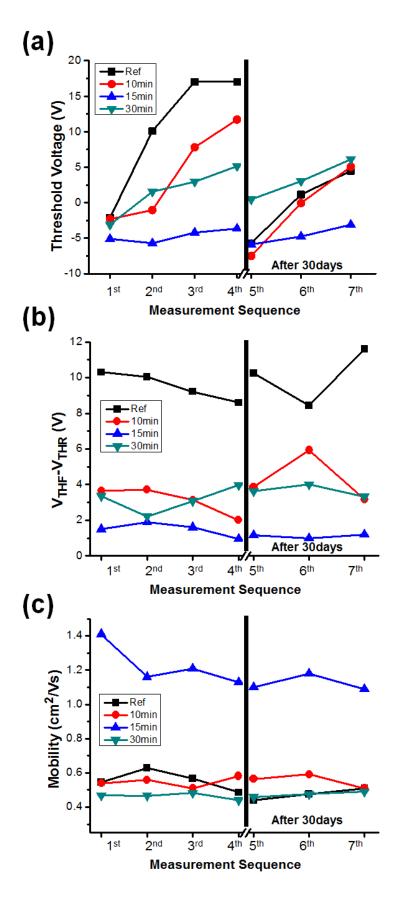

| Figure. 6.4. Transfer characteristics of ZnO TFTs treated with hydrogen plasma for (a) 0 min, (b) 10 min, (c) 15 min, and (d) 30 min as a function of measurement sequence                                                                                                                                        |

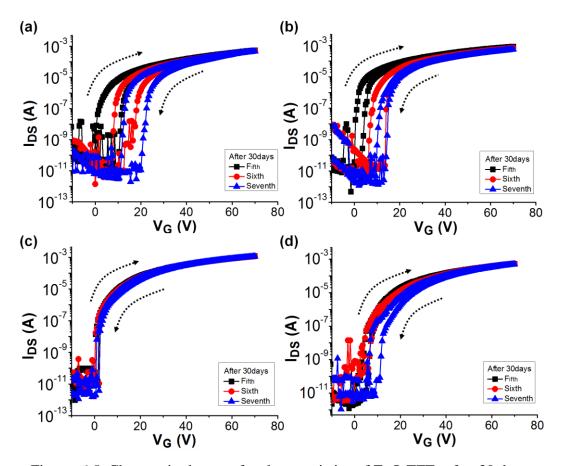

| Figure. 6.5. Changes in the transfer characteristics of ZnO TFTs after 30 days 107                                                                                                                                                                                                                                |

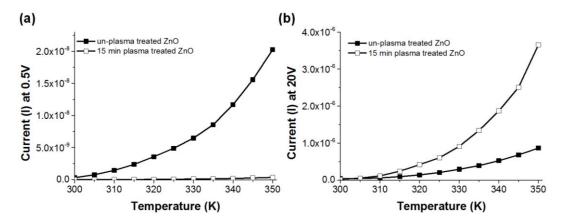

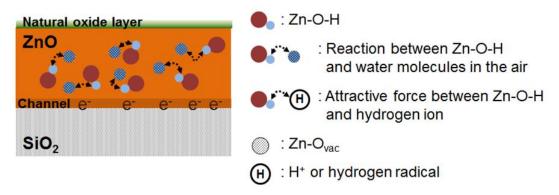

| Figure. 6.6. Comparison of changes in (a) $V_{TH}$ , (b) the $V_{TH}$ difference between forward and reverse scans ( $V_{THF}$ - $V_{THR}$ ) and (c) mobility of ZnO TFTs as a function of the measurement sequence for the various plasma treatment times |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure. 6.7. Model for the interaction between ZnO and hydrogen plasma                                                                                                                                                                                     |

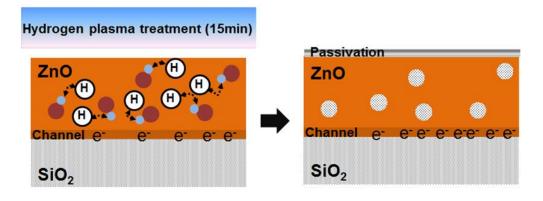

| Figure. 7.1. Schematic diagram of the Al/PMMA/Al structure                                                                                                                                                                                                 |

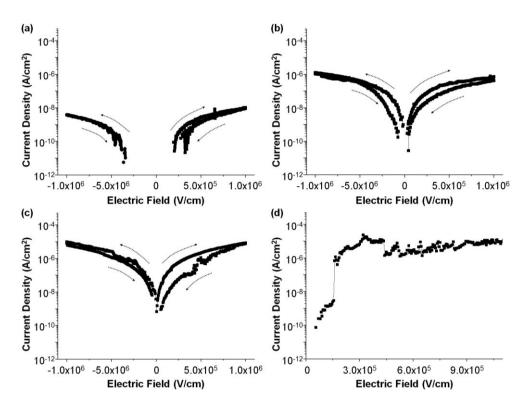

| Figure. 7.2. Current density versus electric field characteristics of (a) PMMA and plasma treated PMMA at (b) 20 W, (c) 40 W and (d) 80 W                                                                                                                  |

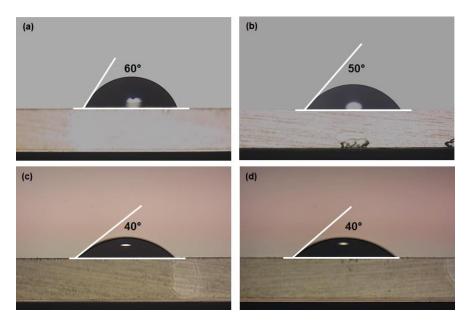

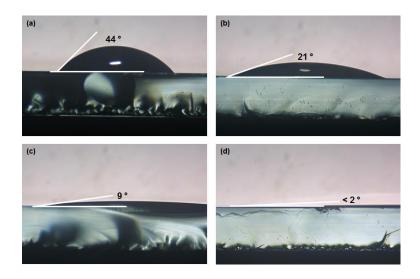

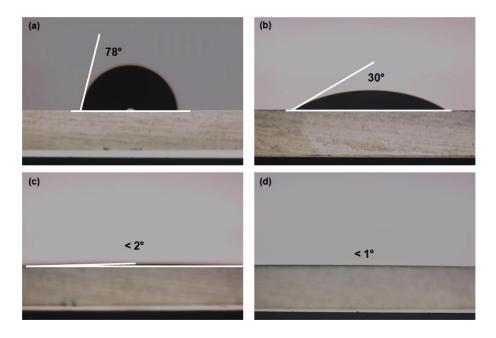

| Figure. 7.3. The contact angles for water measured on (a) untreated PMMA and PMMA treated with oxygen plasma for 10 seconds at power of (b) 20 W, (c) 40 W and (d) 80 W                                                                                    |

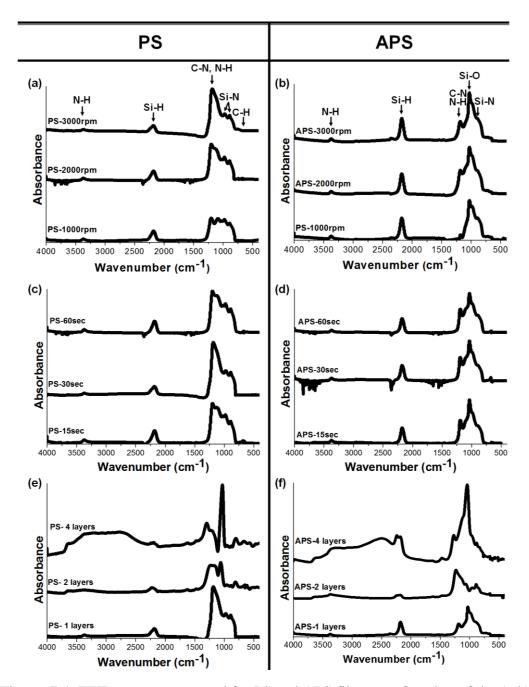

| Figure. 7.4. FTIR spectra measured for PS and APS films as a function of the (a-b) spin coating speed (rpm), (c-d) spin coating time and (e-f) number of spin-coated layers                                                                                |

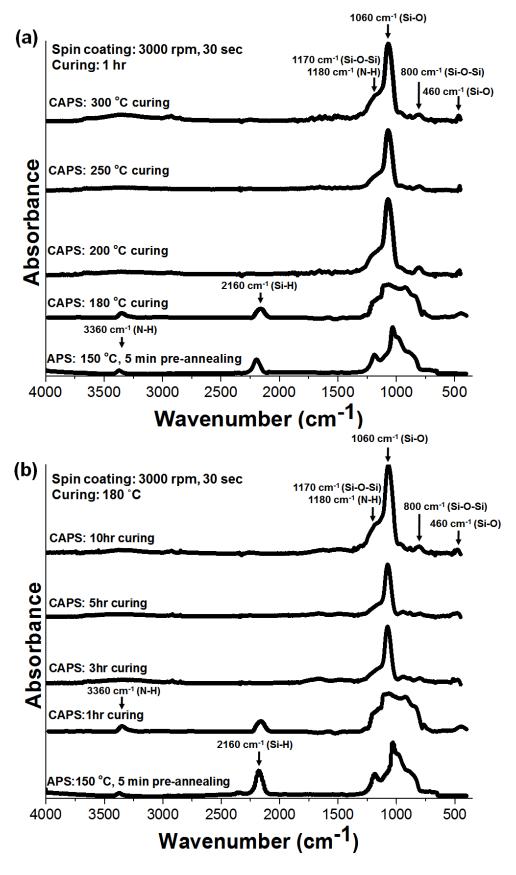

| Figure. 7.5. FTIR absorption of CAPS as a function of (a) curing temperature and (b) curing time                                                                                                                                                           |

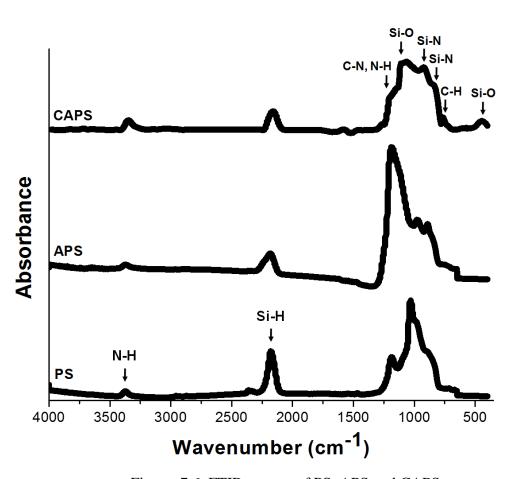

| Figure. 7.6. FTIR spectra of PS, APS and CAPS                                                                                                                                                                                                              |

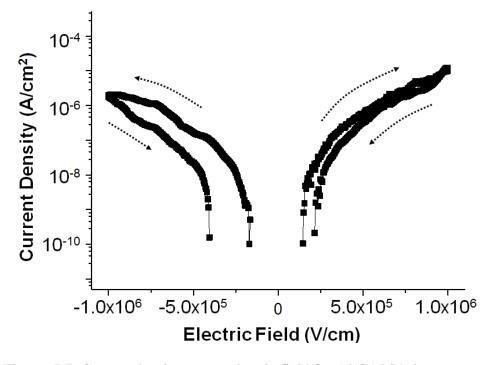

| Figure. 7.7. Current density versus electric field for Al/CAPS/Al structure                                                                                                                                                                                |

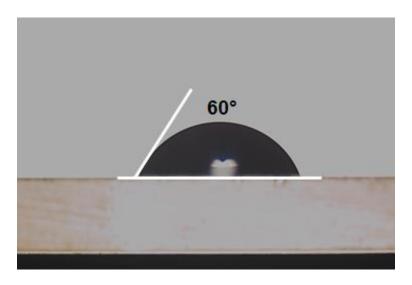

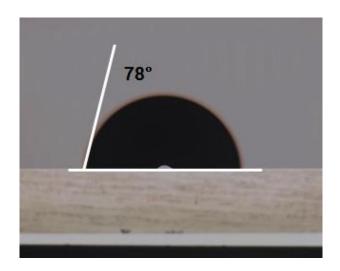

| Figure. 7.8. The contact angle for water measured on cured PHPS                                                                                                                                                                                            |

| Figure. 7.9. The contact angles for water measured on (a) untreated Si, plasma treated Si placed on the (b) top shelf (c) middle shelf and (d) bottom shelf of YES-R3 plasma system.                                                                       |

| Figure. 7.10. The contact angles for water measured on (a) CAPS and OCAPS with plasma treatment at (b) 20 W, (c) 40 W and (d) 80 W for 10 sec                                                                                                              |

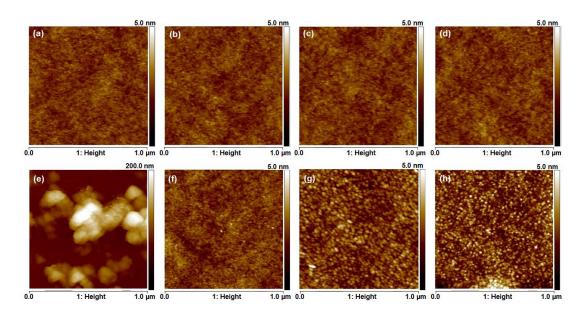

| Figure. 7.11. AFM topography images of (a) CAPS and (b) 20 W, (c) 40 W and (d) 80 W OCAPS films on Al. AFM topography images of ZnO thin films spin-coated onto (e) CAPS/Al and (f) 20 W, (g) 40 W and (h) 80 W OCAPS/Al                                   |

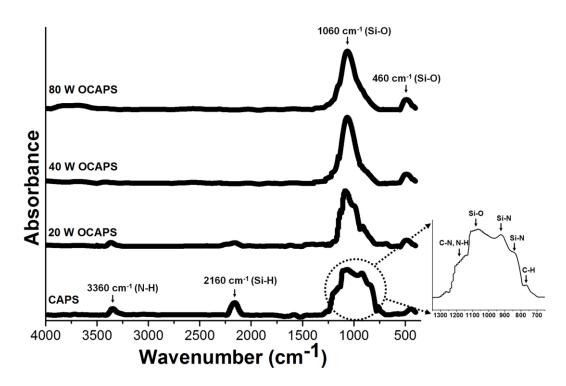

| Figure. 7.12. FTIR spectra measured for OCAPS films as a function of the plasma RF power                                                                                                                                                                   |

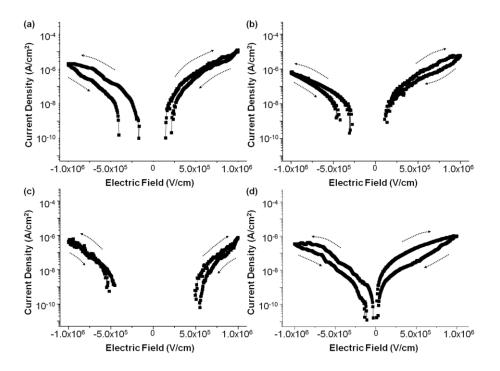

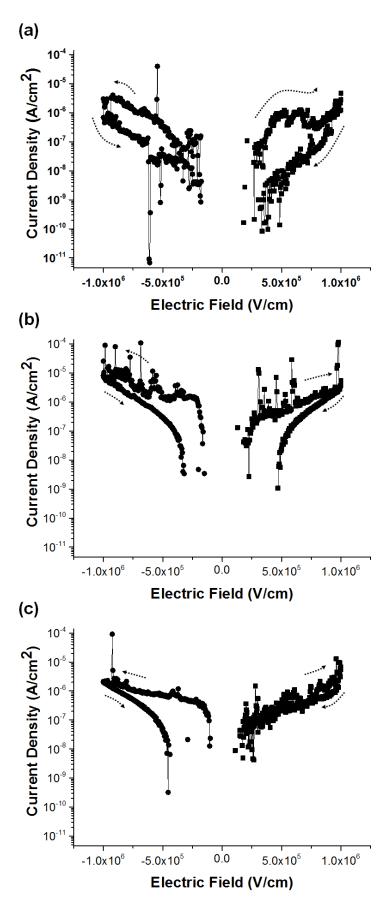

| Figure. 7.13. Current density versus electric field characteristics of Al/insulator/Al structures: (a) reference CAPS and (b) 20 W, (c) 40 W and (d) 80 W OCAPS films.                                                                                     |

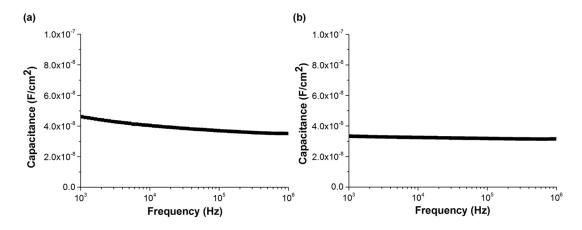

| Figure. 7.14. Capacitance per unit area as a function of frequency for CAPS and 40W OCAPS films. CAPS film thickness = 153 nm; 40 W OCAPS film thickness = 165 nm. 136                                                                                     |

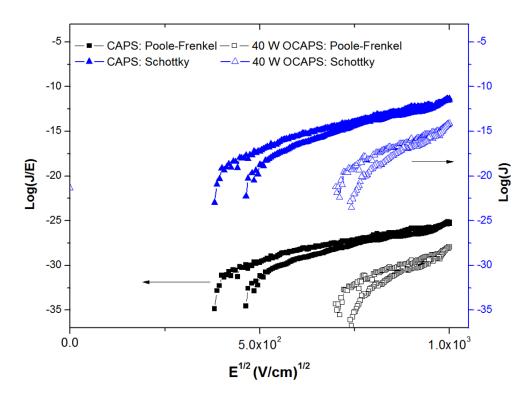

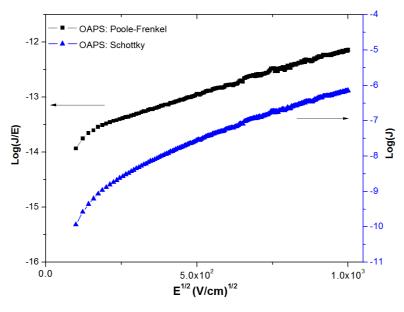

| Figure. 7.15. Schottky ( $ln(J)$ vs $E^{1/2}$ ) and Poole-Frenkel ( $ln(J/E)$ vs $E^{1/2}$ ) plots for CAPS and 40 W OCAPS. Data are shown for forward and reverse voltage scans. 138                                                                      |

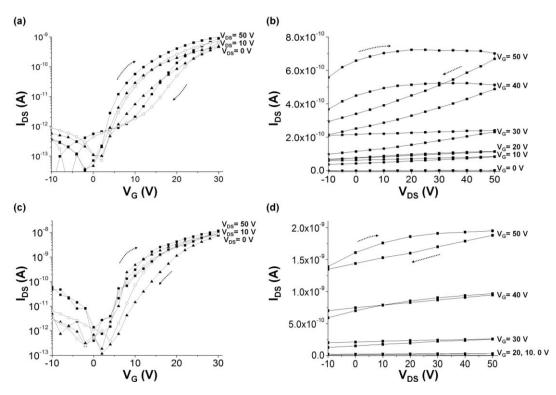

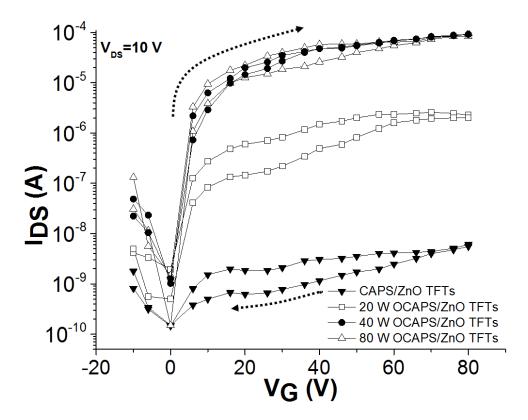

| Figure. 7.16. Transfer characteristics in the linear region ( $V_{DS}$ =10 V) for ZnO TFTs using CAPS and OCAPS films with various plasma treatment powers                                                                                                                                                                                               |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

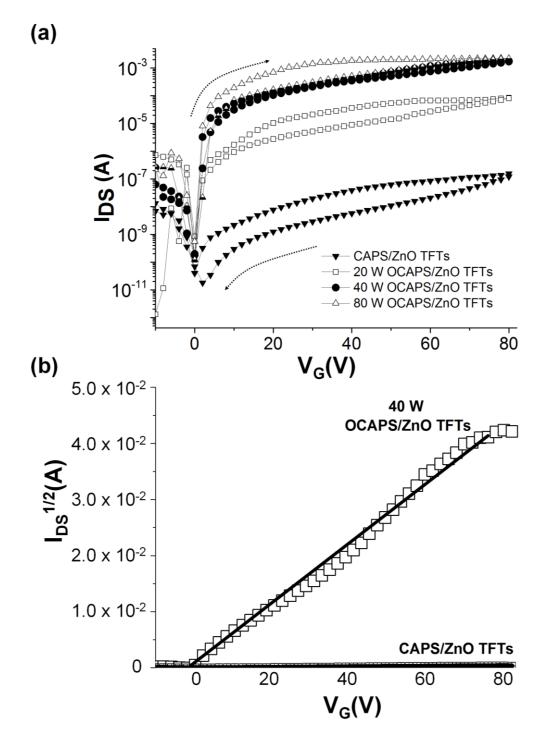

| Figure. 7.17. (a) Transfer characteristics of CAPS/ZnO TFTs, measured at $V_{DS} = 50$ V, with various plasma treatment powers. Data are shown for forward and reverse voltage scans. (b) Plots of $(I_{DS})^{1/2}$ versus $V_G$ for CAPS/ZnO and 40 W OCAPS/ZnO TFTs (forward scans). The full lines are best straight line fits to the data points 142 |

| Figure. 7.18. Output characteristics ( $I_{DS}$ vs $V_{DS}$ curves) of (a) CAPS and (b) 20 W, (c) 40 W and (d) 80 W OCAPS/ZnO TFTs. Data for each $V_G$ value are shown for forward and reverse $V_{DS}$ scans.                                                                                                                                          |

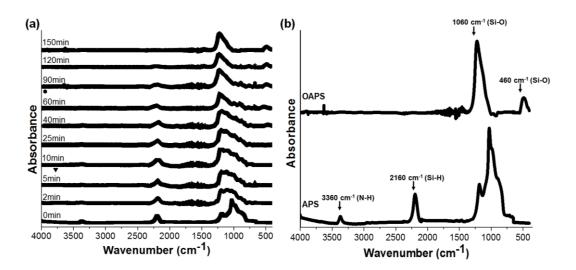

| Figure. 7.19. Change of FTIR spectra of (a) an APS film according to plasma treatment time, (b) APS and an OAPS film after an oxygen plasma treatment for 150 min                                                                                                                                                                                        |

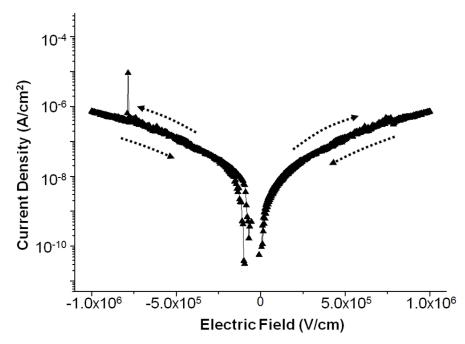

| Figure. 7.20. Current density versus electric field for OAPS with plasma treatment for 150 min. Data are shown for forward and reverse voltage scans                                                                                                                                                                                                     |

| Figure. 7.21. Schottky ( $ln(J)$ vs $E^{1/2}$ ) and Poole-Frenkel ( $ln(J/E)$ vs $E^{1/2}$ ) plots for OAPS (plasma treatment for 150 min). Data are shown for the forward voltage scan.                                                                                                                                                                 |

| Figure. 7.22. (a) Transfer and (b) output characteristics of a ZnO TFT using APS with plasma treatment for 150 min as the gate insulator. Data are shown for forward and reverse voltage scans                                                                                                                                                           |

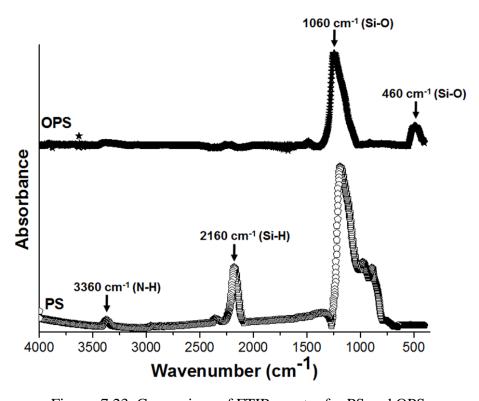

| Figure. 7.23. Comparison of FTIR spectra for PS and OPS                                                                                                                                                                                                                                                                                                  |

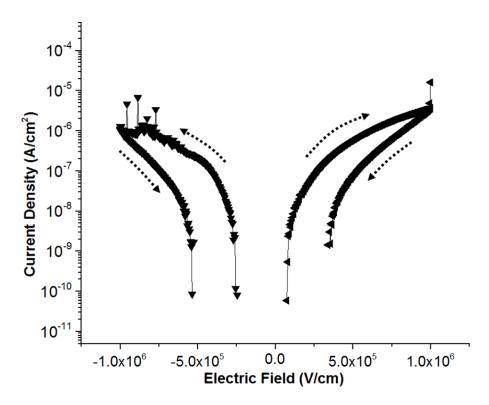

| Figure. 7.24. Current density versus electric field for Al/OPS/Al structure 149                                                                                                                                                                                                                                                                          |

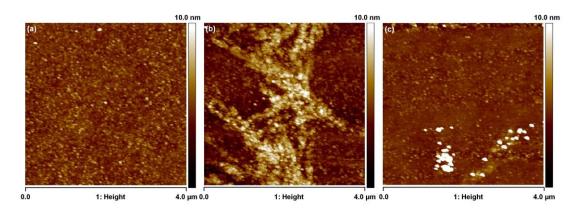

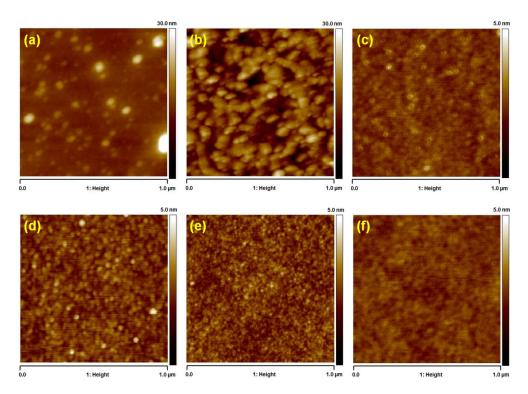

| Figure. 8.1. AFM image of the surface of solution-processed ZnO films (a) before and after immersion into (b) developer and (c) Al etch                                                                                                                                                                                                                  |

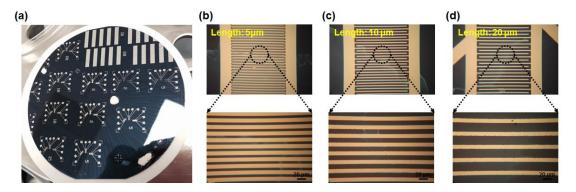

| Figure. 8.2. (a) Photograph of BG-BC ZnO TFTs fabricated onto thermally grown SiO <sub>2</sub> and (b-d) low and high magnification optical micrographs of S/D patterns with various channel lengths                                                                                                                                                     |

| Figure. 8.3. AFM topography image of ZnO spin coated onto the gap between S/D electrodes measured at (a-c) coated region and (d-f) uncoated region                                                                                                                                                                                                       |

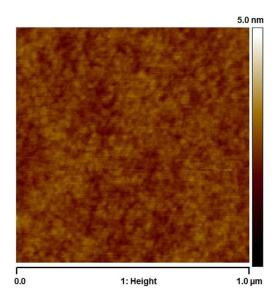

| Figure. 8.4. AFM topography image of thermally grown SiO <sub>2</sub> on a Si substrate 158                                                                                                                                                                                                                                                              |

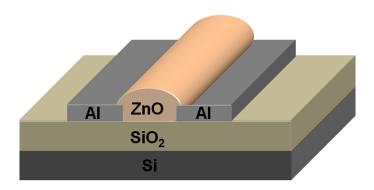

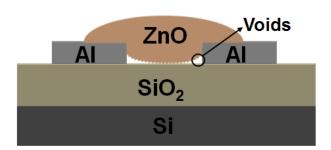

| Figure. 8.5. Schematic structure of solution-processed ZnO TFTs deposited by drop-casting                                                                                                                                                                                                                                                                |

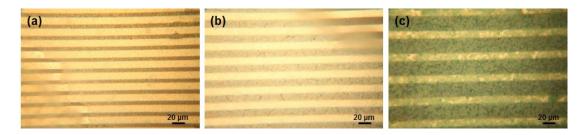

| Figure. 8.6. Optical microscopy images of S/D patterns with (a) 5 μm (b) 10 μm and (c) 20 μm length after the deposition of ZnO by drop-casting                                                                                                                                                                                                          |

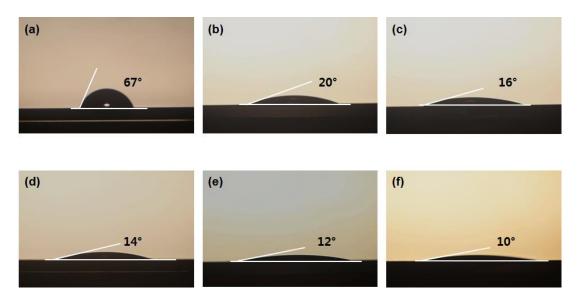

| Figure. 8.7. The contact angles for water measured on thermally grown SiO <sub>2</sub> with plasma treatment at 100 W for (a) 0 min (b) 2 min (c) 5 min (d) 10 min (e) 20 min and (f) 30 min                                                                                                                                                             |

| Figure. 8.8. Possible ZnO TFT architecture following deposition of ZnO by drop-<br>casting                                                                                                                                                    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

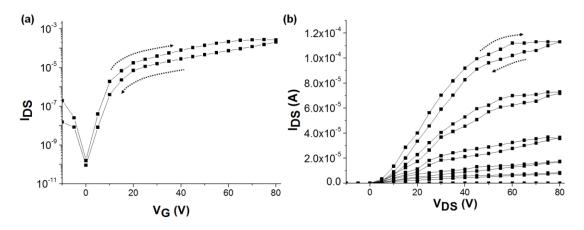

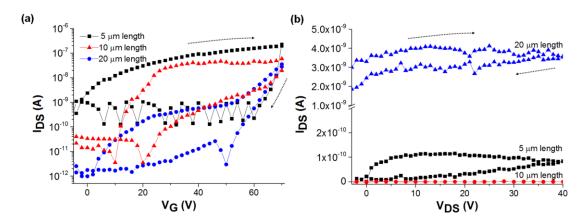

| Figure. 8.9. (a) Transfer ( $I_{DS}$ versus $V_G$ ) and (b) output ( $I_{DS}$ versus $V_{DS}$ ) characteristics of TFTs with drop-cast ZnO/thermally grown SiO <sub>2</sub> and different channel lengths                                     |

| Figure. 8.10. AFM topography images of (a) CAPS and CAPS immersed into (b) developer and (c) Al etch                                                                                                                                          |

| Figure. 8.11. Current density versus electric field characteristics of (a) CAPS and CAPS after exposure to (b) developer and (c) Al etch                                                                                                      |

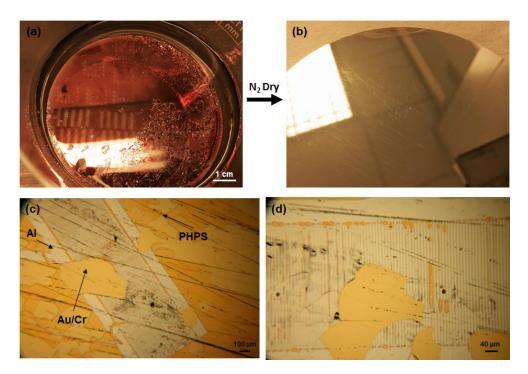

| Figure. 8.12. Optical images of Au/Cr gate substrate (a) during and (b) after the development step in photolithography. (c-d) Optical microscopy images of photolithography-fabricated Al S/D on PHPS/Au/Cr after the Al etching process. 166 |

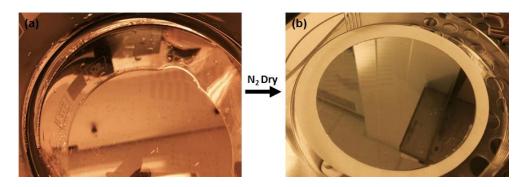

| Figure. 8.13. Images of Al gate substrate (a) during and (b) after the development step                                                                                                                                                       |

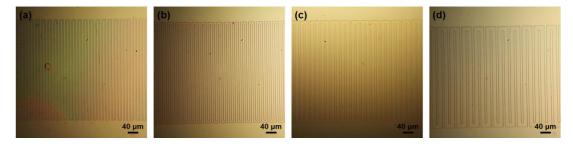

| Figure. 8.14. Optical images of source and drain patterns defined by photolithography with (a) 5 μm (b) 10 μm (c) 15 μm and (d) 20 μm channel lengths                                                                                         |

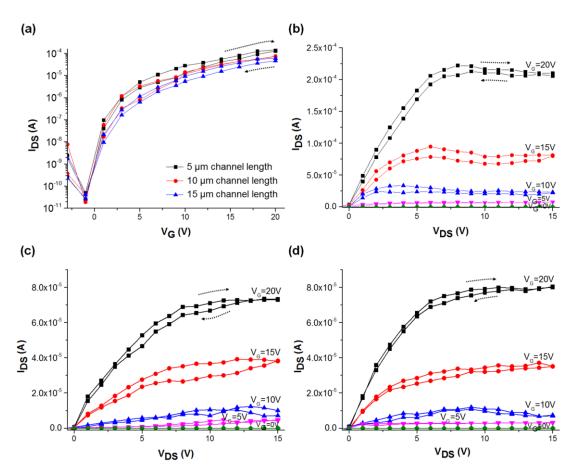

| Figure. 8.15. (a) Transfer ( $I_{DS}$ vs $V_G$ ) and output ( $I_{DS}$ vs $V_{DS}$ ) characteristics of TFTs with channel lengths of (b) 5 $\mu$ m, (c) 10 $\mu$ m and (d) 15 $\mu$ m                                                         |

# **List of Tables**

| Table. 2.1. Overview of inorganic insulators. 4                                                                                            |

|--------------------------------------------------------------------------------------------------------------------------------------------|

| Table. 2.2. Overview of organic insulators. <sup>5</sup> 15                                                                                |

| Table. 2.3. Vacuum-processed ZnO TFTs with various vacuum-processed insulators.                                                            |

| Table. 2.4. ZnO TFTs with various insulators using solution processing for either the semiconductor and/or the insulator                   |

| Table. 3.1. Composition of the two solutions used in this work                                                                             |

| Table. 3.2. Channel dimensions of shadow mask                                                                                              |

| Table. 3.3. List of key equations57                                                                                                        |

| Table 4.1. Activation energy summary of solution-processed ZnO films before and after oxygen plasma treatment77                            |

| Table. 5.1. Summary of the electrical characteristics of a ZnO TFT as a function of measurement conditions                                 |

| Table. 6.1. Subthreshold swing (SS) and interface trap density ( $D_{it}$ ) for ZnO TFTs treated with hydrogen plasma for different times. |

| Table. 7.1. IR peak assignments124                                                                                                         |

| Table.7.2. Summary of the electrical performance of ZnO TFTs143                                                                            |

| Table. 8.1. Summary of the electrical properties of short channel ZnO TFTs with various channel lengths168                                 |

# **Declaration**

I hereby declare that the work carried out in this thesis has not been previously submitted for any degree and is not currently being submitted in candidature for any other degree.

Y. Jeong

February 2016

# **Copyright © 2016 by Yesul Jeong**

The copyright of this thesis rests with the author. No quotation from it should be published without the prior written consent and information derived from it should be acknowledged.

## Acknowledgements

I would like to provide grateful acknowledgements to the following people:

It would have been impossible to finish my work without the help from my supervisors, Prof Michael C. Petty and Dr Chris Pearson. I would like to express my extreme gratitude to my first supervisor, Prof Michael C. Petty. He guided me based on his abundant teaching experience and always gave me his precious time for support and discussion concerning my research, as well as help with my personal issues. I would also like to thank my second supervisor, Dr Chris Pearson. There is no doubt in my mind that his valuable advice and guidance on many experimental techniques have helped further my research smoothly. Once again, I am profoundly indebted to both of them.

Ministry of Knowledge Economy (Korea, Industrial Strategic Technology Development Program) and Centre for Process Innovation (CPI, UK) have provided tuition fees and living expenses. School of Engineering and Computing Sciences, Durham University also has provided tuition fees and living expenses in Year 3. I would not have been able to achieve this thesis without their financial support.

I would also like to express my sincere thanks to all members of the Centre for Molecular and Nanoscale Electronics. They provided a friendly environment and helped me adapt myself to a new environment abroad fairly well. Additionally, they gladly helped me with experimental work in the cleanroom and shared their useful experimental knowledge and experience. My gratitude also goes to all the current and former colleagues outside of my research group. I would like to particularly

thank Yeongeun Jeon, Bushra Al-sulaimi and Anum Dada. They listened attentively to my worries and sincerely encouraged me.

This work is partially integrated in the research project of Centre for Process Innovation Limited, which makes this thesis more comprehensive. My thanks go especially to Dr Yong Uk Lee for giving not only beneficial advice about my research but also advice for daily life, and also to Dr Simon Ogier for valuable discussions.

I am grateful for the support of the project members in Korea, including Dr. Lee-Mi Do of the Electronics and Telecommunications Research Institution (ETRI), Prof. Hongdoo Kim of Kyung Hee University and Man-Young Park of DNF Co. Ltd.

Many thanks to members of the Korean community that I have met during my time in Durham. They are deeply compassionate and lavished me with affection. In particular I must thank Bong Sun Park, Chin Hun Chung, Ki Ho Lee, Jaeun Yun, Ki Hwan Song, Jeong Gi Min and Jeongin Kwon. My life in Durham has been enjoyable because I have met these congenial friends.

마지막으로, 존재만으로도 너무나도 힘이 되는 부모님께 감사의 말씀을 전하고 싶습니다. 그 동안 당연하게 누려왔던 모든 것들이 두분의 딸로 태어나 살아갈수 있었기에 가능했습니다. 항상 고맙고 존경하고 사랑합니다.

## Chapter 1

## Introduction

The requirements of modern display technology include high resolution, large area, transparency, flexibility and low cost. To date, active-matrix flat panel displays (AM-FPDs) have dominated the market. These architectures possess a number of advantages. They are thin and light weight and produce high-resolution images. Consequently, these have been used in applications such as monitors, televisions and portable devices. The displays can be classified by the materials used and the method of display. Active-matrix liquid crystal displays (AMLCDs) and active matrix organic light emitting diode (AMOLED) displays are examples of typical technologies. Thin film transistors (TFTs) have a strong influence on the image quality and performance of such displays by controlling the switching of pixels.

In order to realise large-volume, flexible electronics, current TFT research is focused on the improvement of materials and processing techniques. Process development is mainly categorised according to vacuum and non-vacuum deposition (solution-processing). Material development can be divided into semiconductor, gate dielectric, electrode and passivation materials. Hydrogenated amorphous Si (a-Si:H)<sup>6,7</sup> satisfies the various requirements for application as the active channel layer

in TFTs. These include processing below 300 °C on large area glass substrates, low fabrication cost and excellent uniformity. Since Spear and LeComber explored a-Si:H in 1975, large area displays based on AMLCDs have seen major improvements. However, devices based on a-Si:H suffer from low carrier mobilities (~ 0.5 cm²/Vs) and poor stability. Poly-Si provides an alternative with improved switching speeds, high field effect mobilities (30~500 cm²/Vs) and good stability. Poly-Si is manufactured by the recrystallisation of a-Si:H. Laser annealing, rapid thermal annealing and metal induced thermal annealing are used as additional process steps, which lead to increased fabrication costs and reduce the process yield.

Organic semiconductors<sup>12,13</sup> are excellent candidates for future displays due to their simple low temperature processing and mechanical flexibility. Nevertheless, their electrical performance, sensitivity to the environment and stability still need to be improved.

ZnO<sup>14-17</sup> is also a promising candidate for use as the semiconductor in TFTs, as evidenced by its commercial applications. There are a number of reasons for this: the raw materials are cheap and abundant; ZnO is nontoxic; it has excellent optical transparency and high carrier mobility compared to other semiconductors materials. Finally, ZnO has the potential for low temperature processing. Therefore, ZnO has been widely investigated as a potential replacement for Si-based materials (such as a a-Si:H and poly Si) and organic semiconductors.

The gate insulator directly impacts on the electrical properties of TFTs by influencing the charge carrier density accumulated in the semiconductor channel. Gate dielectrics possessing a large permittivity, low leakage current densities and an optimised structure with a smooth interface are essential in order to realise high-

performance TFTs. Gate insulators can be categorised by material type, such as inorganic, organic or hybrid gate. Polymer or self-assembled mono- and multilayers are examples of organic dielectrics, and the use of both organic and inorganic materials together constitutes a hybrid gate insulator. Over several decades, silicon dioxide (SiO<sub>2</sub>), which is a typical inorganic gate insulator, has been intensively studied for application in TFTs. Consequently, it has been successfully commercialised in display devices. However, the production costs are relatively high resulting from the need for a vacuum system. Moreover, high-temperature processing is required, which limits applications in advanced future display technologies such as flexible or transparent applications.

This thesis mainly focuses on solution-processed TFTs fabricated at temperatures below 150 °C. This work was supported by the Industrial Strategic Technology Development Program (10041808, Synthesis of Oxide Semiconductor and Insulator Ink Materials and Process Development for Printed Backplane of Flexible Displays Processed Below 150 °C) funded by the Ministry of Knowledge Economy (MKE, Korea). The project is comprised of eight institutions; Electronics and Telecommunications Research Institution (ETRI) (co-ordinator), Durham University (study of solution-processed ZnO TFTs), Inha University (study of gate insulator materials), Yonsei University (study of solution-processed ZnO TFTs), Kyunghee University (study of semiconductor materials), DNF Co., Ltd (industrialisation of gate insulator materials), Philostone (industrialisation of semiconductor materials) and Kumchang E&I Co.,Ltd (industrialisation of post-deposition processing). This work was also partially integrated in the collaborative research project (Short channel solution-processed ZnO TFTs), funded by The Centre for Process Innovation (CPI). The Final objective of this project is to develop

a transistor with useful electrical properties fabricated by solution processing at low temperature (maximum 150 °C) to apply to a flexible substrate. However, this thesis is mainly focused on the development of solution processable materials for the semiconductor and insulator layers. The analysis of the device performance provides the basis for future work on solution-processed transistors fabricated on flexible substrates. The work falls into three parts. First, ZnO is adopted as the semiconductor layer. Films are fabricated by solution processing techniques such as spin-coating or spray pyrolysis. Secondly, solution-processed SiO<sub>2</sub> is explored as the gate insulator and its application in solution-processed ZnO TFTs is studied. Thirdly, plasma treatment is utilised for post deposition processing to improve the film properties and reduce the processing temperature.

The thesis is organised into the following sections. Chapter 2 provides a literature review of previous work on ZnO TFTs, including fabrication methods, experimental conditions and device properties. The experimental details for this work are given in Chapter 3. The results are presented in the subsequent five chapters. Chapter 4 is concerned with the electrical conduction mechanisms present in solution-processed ZnO films. Chapter 5 describes the optimisation of the fabrication conditions for solution-processed ZnO films by chemical spray pyrolysis. The resulting conditions are used for spray-coated ZnO TFTs, and their electrical performance and stability are discussed. Chapter 6 deals with the processing methods used to influence the electrical properties of solution-processed ZnO TFTs. Hydrogen plasma treatment is proposed as a post-deposition processing technique to improve the electrical performance and stability. In Chapter 7, spin-coated PHPS with a maximum processing temperature of 180 °C is explored. To accelerate the conversion into SiO<sub>2</sub>, oxygen plasma treatment is used. Film properties including

morphology, chemical and electrical characteristics are investigated as a function of plasma treatment power. Thin film transistors are fabricated to confirm the performance of a spin-coated SiO<sub>2</sub> layer as a good gate insulator. The investigation of the effects of small channel dimensions on solution-processed ZnO TFTs is described in Chapter 8. The process development for photolithographically defined source and drain electrodes in solution-processed ZnO TFTs and the resulting changes in electrical performance are reported. Finally, Chapter 10 summarises and concludes this work and provides suggestions for further research.

#### References

- 1. L. F. Weber, IEEE Trans. Electron Dev. 24 (7), 864 (1977).

- 2. A. Dodabalapur, Solid State Commun. 102 (2-3) 259 (1997).

- W. B. Choi, D. S. Chung, J. H. Kang, H. Y. Kim, Y. W. Jin, I. T. Han, Y. H. Lee,

J. E. Jung, N. S. Lee, G. S. Park, and J. M. Kim, Appl. Phys. Lett. 75, 3129 (1999).

- H. Meiling, J. F. M. Westendorp, J. Hautala, Z. M. Saleh, and C. T. Malone, MRS Proceedings, 345, 65 (1994).

- 5. C. Chen and J. Kanicki, IEEE Electron Device Lett. 17, 437 (1996).

- 6. A. V. Gelatos and J. Kanicki, Appl. Phys. Lett. 57 (12), 1197 (1990).

- K. S. Karim, A. Nathan, M. Hack, and W. I. Milne, IEEE Electron Device Lett.

25 (4), 188 (2004).

- 8. A. Nathan, G. R. Chaji, and S. J. Ashtiani, J. Display Technol. 1 (2), 267 (2005).

- 9. C. R. Kagan and P. Andray, Marcel Dekker, Inc. New York (2009).

- 10. Y. Kuo, Kluwer Academic Publishers, Boston (2004).

- 11. W. E. Spear and P. G. LeComber, Solid State Commun. 17 (9), 1193 (1975).

- J. Kim, J. Jeong, H. D. Cho, C. Lee, S. O. Kim, S.-K. Kwon, and Y. Hong, J. Phys. D: Appl. Phys. 42 (11), 115107 (2009).

- 13. Y. Yun, C. Pearson, and M. C. Petty, J. Appl. Phys. 105 (3), 034508 (2009).

- E. M. C. Fortunato, P. M. C. Barquinha, A. C. M. B. G. Pimentel, A. M. F. Goncalves, A. J. S. Marques, L. M. N. Pereira, and R. F. P. Martins, Adv. Mater. 17 (5), 590 (2005).

- T. Kamiya, K. Nomura, and H. Hosono, Sci. Technol. Adv. Mater. 11 (4), 044305 (2010).

- 16. S. R. Thomas, P. Pattanasattayavong, and T. D. Anthopoulos, Chem. Soc. Rev. 42 (16), 6910 (2013).

- 17. A. Janotti and C. G. V. Walle, Rep. Prog. Phys. 72 (12), 126501 (2009).

## **Chapter 2**

## **Thin Film Transistors**

This chapter provides an overview of thin film transistors. The fundamental concepts of devices and materials are introduced, followed by a discussion of vacuum-processed ZnO TFTs. Finally, a review of solution-processed ZnO TFTs is presented.

#### 2.1 Operation of TFTs

#### 2.1.1 Physics of Thin Film Transistors

There are four main types of TFT architecture, depending on the relative position of each layer and the fabrication sequence, as shown in Fig. 2.1. In the bottom gate structures, depicted in Fig. 2.1(a) and (b), the active (semiconductive) layer is deposited after the gate and gate insulator layers, which tend to be more stable than the active layer. This means that damage to the interface where the channel is formed will be minimised. However, exposure of the top surface of the active layer to the environment can lead to device degradation, and the device needs an additional passivation process. The top gate structures, shown in Fig. 2.1(c) and (d), can reduce or eliminate this problem, because the active layer is placed beneath the gate insulator. Hence the surface of the active layer is inherently passivated. The bottom

gate, top contact structure, as shown in the Fig. 2.1(a), is commonly used as a switching device in flat panel displays (FPDs) while poly-Si TFTs exploit the top gate, top contact configuration (Fig. 2.1(d)) because of additional ion doping and activation processes. Devices fabricated by direct printing methods, such as inkjet printing or spray pyrolysis, usually adopt the bottom gate, bottom contact architecture, Fig. 2.1(b).

Figure. 2.1. Four possible TFT structures: (a) bottom gate, top contact, (b) bottom gate, bottom contact, (c) top gate, bottom contact, and (d) top gate, top contact.

The operation of an n-type TFT can be described as follows. A positive voltage is applied to the gate. This induces negative carriers to accumulate in the semiconductor at the dielectric/semiconductor interface which provides a conducting channel. At low drain voltages, the current flowing through the channel,  $I_{DS}$ , follows

Ohm's law, i.e.,  $I_{DS} = V_{DS}/R(V_G)$ , where  $R(V_G)$  is the resistance of the channel and  $V_{DS}$  is drain-to-source voltage. This operation mode is called the linear regime, as shown in Fig. 2.2(a). The drain-source current,  $I_{DS,lin}$  can be described by

$$I_{DS,lin} = \mu_{FE} C_i \frac{W}{L} \left( V_G - V_{TH} - \frac{V_{DS}}{2} \right) V_{DS}$$

(2.1)

where  $V_G$  is the gate voltage, W and L are the channel width and length respectively,  $C_i$  is the capacitance per unit area of the insulator layer,  $V_{TH}$  is the threshold voltage and  $\mu_{FE}$  is the field effect mobility.

As the magnitude of the applied positive  $V_{DS}$  increases, so that  $V_{DS}$  is not negligible compared to the voltage  $(V_G - V_{TH})$ ,  $I_{DS}$  versus  $V_{DS}$  is no longer Ohmic, and channel pinch-off occurs. This is called saturation operation, as depicted in Fig. 2.2(b). In the saturation region, the drain current,  $I_{DS,Sat}$ , can be expressed by

$$I_{DS,sat} = \frac{1}{2} \mu_{FE} C_i \frac{W}{L} (V_G - V_{TH})^2$$

(2.2)

Transistor parameters can be extracted from the current versus voltage Eqns. 2.1 and 2.2. The key factors determining device performance are the on/off current ratio  $(I_{ON}/I_{OFF})$ , the threshold voltage  $(V_{TH})$  and carrier mobility  $(\mu_{FE})$ . A good TFT possesses a high on-current, a high on/off ratio,  $V_{TH}$  close to 0 V and a high mobility. The on/off ratio can be determined by the highest  $I_{ON}$  over the lowest  $I_{OFF}$ . The values of  $V_{TH}$  and mobility in the saturation region can be extracted from the slope and x-intercept, respectively, of a plot of  $(I_{DS,Sat})^{1/2}$  versus  $V_G$ .

Figure. 2.2. Ideal n-type TFT operation: (a) linear region, and (b) saturation region.

#### 2.1.2 Semiconductor

Oxide materials have traditionally been used as gate insulators due to their wide band gaps. However, in the case of certain heavy-metal oxides (e.g.  $InO_3$ ,  $SnO_2$  and ZnO), the metal cations exhibit large spherical s-orbitals, leading to direct overlap between neighbouring atoms and resulting in semiconducting behaviour. Figure 2.3 compares the electronic structure of silicon and metal oxide semiconductors. In the case of the latter, a significant overlap between neighbouring atoms allows variations in bond angles without significant deterioration of the charge carrier mobility and with a structural change from crystalline to amorphous states (Fig. 2.3(b)). For example, the metal oxide semiconductor indium-gallium-zinc oxide (InGaZnO) exhibits a mobility of  $\sim 80~cm^2/Vs$  and  $\sim 10~cm^2/Vs$  for its crystalline and amorphous states,

respectively.  $^{1,2}$  This change is small compared to the decrease seen with silicon, from  $1000 \text{ cm}^2/\text{Vs}$  for single crystal to  $1 \text{ cm}^2/\text{Vs}$  for amorphous material.

The advantages of metal oxide semiconductors can be summarised:

- Good electrical properties, even when fabricated at low/room temperature (cf the degradation of the electrical properties of amorphous Si fabricated at < 250 °C).

- Relatively high carrier mobility in the amorphous state (>  $10 \text{ cm}^2/\text{Vs}$ ) (cf amorphous Si:  $< 1 \text{ cm}^2/\text{Vs}$ ).

- Effective improvement of the electrical characteristics by doping with Group III elements such as indium, gallium or tin.

- Defect deactivation processing is unnecessary (amorphous Si requires hydrogenation to eliminate dangling bonds).

Figure. 2.3. Comparison of atomic orbital overlap in crystalline and amorphous semiconductors for (a) silicon and (b) metal oxide semiconductor. <sup>2,3</sup>

#### 2.1.3 Gate Insulator

A channel for carrier transport in TFTs is generated at the interface between the semiconductor and dielectric. This means that device performance is directly related to the properties of the gate insulator. In terms of TFTs with bottom gate, top contact and bottom gate, bottom contact structures, the morphology of the gate insulator affects that of the subsequent semiconductor layer. For example, a gate insulator with a rough surface leads to an uneven interface between the gate insulator and semiconductor, resulting in poor device performance. In a TFT, the current through the channel is proportional to the gate capacitance per unit area, and to the voltage applied to the electrodes (see Eqns. 2.1 and 2.2). Therefore, one important factor that influences device performance is the gate capacitance per unit area,  $C_i$ . If two electrodes are on opposite sides of a dielectric material of thickness d,  $C_i$  is defined as

$$C_i = \varepsilon_0 \frac{k}{d} \tag{2.3}$$

where  $\varepsilon_0$  is the vacuum permittivity, k is the dielectric constant and d is the dielectric thickness.

Various materials have been studied in the search for a good gate insulator. These can be divided into two major groups: inorganic and organic compounds. Representative inorganic materials are listed in Table 2.1. Silicon oxide has been widely used as a gate insulator because of its advantages such as high resistivity, good thin film uniformity and the formation of a stable interface with a Si substrate. As evident in Eqn. 2.3,  $C_i$  is inversely proportional to the insulator thickness and directly proportional to k. The problem of using thickness control to achieve high  $C_i$  is that the leakage current increases as the thickness is decreased. High-k materials

such as  $Al_2O_3$ ,  $ZrO_2$  and  $HfO_2$  are good candidates to provide high  $C_i$  values without the requirement for the insulator layer to be very thin. Although inorganic materials have successfully been adopted for use in transistors, these are invariably processed under vacuum and/or at high temperature. Organic insulators are alternatives to inorganic insulators with the added advantage of solution processing by spin-coating or printing at low temperature. Popular organic insulators and their dielectric constants are listed in Table 2.2.

Table. 2.1. Overview of inorganic insulators.<sup>4</sup>

| Materials          | Dielectric<br>Constant (k) | Dielectric<br>strength<br>(kV/mm) | Volume<br>Resistivity<br>(Ω·cm) |

|--------------------|----------------------------|-----------------------------------|---------------------------------|

| $SiO_2$            | 3.9                        | 470~670                           | $10^{14} \sim 10^{17}$          |

| $Si_3N_4$          | 7                          | 20                                | $10^{14} \sim 10^{17}$          |

| $Al_2O_3$          | 9                          | 15                                | $10^{14}$                       |

| $Ta_2O_5$          | 22                         | -                                 | -                               |

| $TiO_2$            | 80                         | 4                                 | $10^{12}$                       |

| SrTiO <sub>3</sub> | 2000                       | -                                 | -                               |

| $ZrO_2$            | 25                         | 10                                | >104                            |

| $HfO_2$            | 25                         | 10                                | >104                            |

| HfSiO <sub>4</sub> | 11                         | -                                 | -                               |

| $La_2O_3$          | 30                         | 2-4                               | -                               |

| $Y_2O_3$           | 15                         | 2.55                              | -                               |

| LaAlO <sub>3</sub> | 30                         | -                                 | -                               |

Table. 2.2. Overview of organic insulators.<sup>5</sup>

| Materials                         | Dielectric<br>Constant<br>(k) | Dielectric<br>strength<br>(kV/mm) | Volume<br>Resistivity<br>(Ω·cm) |

|-----------------------------------|-------------------------------|-----------------------------------|---------------------------------|

| Polycarbonate (PC)                | 2.8                           | 15                                | 10 <sup>17</sup>                |

| Polypropylene (PP)                | 2.2                           | 24                                | 10 <sup>18</sup>                |

| Polyethylene terephthalate (PET)  | 3.3                           | 16                                | 10 <sup>17</sup>                |

| Polyvinylidene fluoride (PVDF)    | 12                            | 13                                | 10 <sup>15</sup>                |

| Polyethylene naphthalate (PEN)    | 3.2                           | 150                               | 10 <sup>17</sup>                |

| Polyphenylene sulphide (PPS)      | 3.0                           | 15                                | 10 <sup>17</sup>                |

| Polyimide (PI)                    | 3.5                           | 150                               | $10^{17}$                       |

| Polymethyl<br>methacrylate (PMMA) | 3.5                           | 20                                | 10 <sup>15</sup>                |

| Polystyrene (PS)                  | 2.6                           | 20                                | -                               |

| Polyethylene (PE)                 | 3.5                           | 19                                | -                               |

| Poly 4-vinylphenol (PVP)          | 4.5                           | -                                 | -                               |

| Benzocyclobutene (BCB)            | 2.65                          | 300                               | 10 <sup>19</sup>                |

## 2.2 Vacuum-processed TFTs

Vacuum techniques such as pulsed laser deposition (PLD), sputtering and atomic layer deposition (ALD) are widely used to fabricate thin films for electronic devices. Since the first ZnO-based TFT was reported in 1968 by Boesen et al.,<sup>6</sup> many studies have focused on the development of ZnO TFTs using vacuum processing. Transparent TFTs have been studied by Masuda et al.,<sup>7</sup> and a ZnO layer fabricated by PLD at 450 °C was adopted as the active layer. Although the transistors showed a

transmittance of more than 80% in the visible region, the electrical performance was poor. Carcia et al.<sup>8</sup> have demonstrated ZnO TFTs deposited on Si substrates by sputtering. The mobility and on/off ratio of these devices were  $1.2 \text{ cm}^2/\text{Vs}$  and  $\sim 10^6$ , respectively. The crucial point to note in this study is that the devices were fabricated at near room temperature, suggesting the potential applications of ZnO TFTs in flexible electronics. In an effort to reduce the process temperature and improve the electrical properties, the development of post-deposition processing has been studied. For example, Chen et al.<sup>9</sup> reported sputter-deposited ZnO TFTs; the ZnO film was deposited at room temperature followed by post-deposition processing with supercritical  $CO_2(scCO_2)$  at  $150 \, ^{\circ}C$ . The device characteristics were improved, showing  $V_{TH}$  of  $27.9 \, \text{V}$ , an on/off ratio of  $\sim 10^6$  and a mobility of  $2.6 \, \text{x} \, 10^{-2} \, \text{cm}^2/\text{Vs}$ .

As the formation of the channel is directly related to the interface between the semiconductor and insulator, the choice of well-matched insulator and semiconductor materials is also crucial. Successful exploitation of the silicon and silicon dioxide (Si/SiO<sub>2</sub>) combination has already been proven in silicon-based TFTs. Furthermore, the properties of silicon dioxide, such as high resistively and low surface roughness, make it ideal as a gate insulator. Consequently, SiO<sub>2</sub> thermally grown or deposited by plasma-enhanced chemical vapour deposition (PECVD) has been extensively used as the gate insulator for ZnO TFTs, with devices generally showing excellent electrical performance with high mobility, on/off ratio and stability. As a result, commercial production of ZnO TFTs has already adopted SiO<sub>2</sub> as the gate insulator. However, with the preference for low temperature processing, the limitations of SiO<sub>2</sub> have become apparent. Other materials that can be used as the gate insulator in ZnO TFTs are high-*k* materials or double layers such as HfO<sub>2</sub>, Al<sub>2</sub>O<sub>3</sub>, Y<sub>2</sub>O<sub>3</sub> Bi<sub>1.5</sub>Zn<sub>1.0</sub>Nb<sub>1.5</sub>O<sub>7</sub> (BZN), (Ba,Sr)TiO<sub>3</sub> (BST), Al<sub>2</sub>O<sub>3</sub>/TiO and

Al<sub>2</sub>O<sub>3</sub>/HfO<sub>2</sub>. Such insulators facilitate relatively thick, pinhole free layers with no reduction of gate capacitance. Sputtering or ALD are widely used as deposition techniques for high-*k* gate insulators.

Table 2.3 provides an overview of vacuum-processed ZnO TFTs reported in the literature. The semiconductor and insulator materials and their fabrication methods are highlighted. The key transistor characteristics such as mobility, on/off ratio and  $V_{TH}$  are listed. The mobility, on/off ratio and  $V_{TH}$  for ZnO TFTs combined with various insulators range from 2.6 x  $10^{-2}$  cm<sup>2</sup>/Vs to 31 cm<sup>2</sup>/Vs,  $10^{3}$  to  $10^{8}$  and -1.0 V to 31 V, suggesting that the electrical properties are strongly dependent on many factors, such as materials, fabrication temperature and deposition method.

Table. 2.3. Vacuum-processed ZnO TFTs with various vacuum-processed insulators.

| Author                            | Semiconductor |            |            | Insulator                                        |            |            | Electrical properties |                                |                           | N.                                                          |

|-----------------------------------|---------------|------------|------------|--------------------------------------------------|------------|------------|-----------------------|--------------------------------|---------------------------|-------------------------------------------------------------|

|                                   | Material      | Method     | Temp. (°C) | Material                                         | Method     | Temp. (°C) | On/Off<br>ratio       | Mobility (cm <sup>2</sup> /Vs) | <i>V<sub>TH</sub></i> (V) | Note                                                        |

| Masuda et al. <sup>7</sup>        | ZnO           | PLD        | 450        | SiO <sub>2</sub> /SiN <sub>x</sub>               | PECVD      | 400/200    | 10 <sup>5</sup>       | 0.97                           | -1.0                      | -                                                           |

| Carcia et al.8                    | ZnO           | Sputtering | RT         | SiO <sub>2</sub>                                 | Thermal    | -          | 10 <sup>6</sup>       | 1.2                            | 0                         | -                                                           |

| Chen et al.9                      | ZnO           | Sputtering | 150        | SiN <sub>x</sub>                                 | PECVD      | -          | 10 <sup>6</sup>       | 2.6x10 <sup>-2</sup>           | 27.9                      | CO <sub>2</sub> (scCO <sub>2</sub> ) Treatment<br>at 150 °C |

| Fortunato et al. <sup>10</sup>    | ZnO           | Sputtering | RT         | Al <sub>2</sub> O <sub>3</sub> /TiO              | Sputtering | RT         | 10 <sup>5</sup>       | 20                             | 21                        | -                                                           |

| Navamathavan et al. <sup>11</sup> | ZnO           | Sputtering | 300        | SiN <sub>x</sub>                                 | PECVD      | 300        | 10 <sup>5</sup>       | 31                             | 9                         | -                                                           |

| Huby et al. <sup>12</sup>         | ZnO           | ALD        | 100        | $Al_2O_3$                                        | ALD        | -          | 10 <sup>7</sup>       | 1                              | 1.8                       | -                                                           |

| Fortunato et al. 13               | ZnO           | Sputtering | RT         | Al <sub>2</sub> O <sub>3</sub> /TiO              | ALD        | -          | 10 <sup>5</sup>       | 27                             | 19                        | -                                                           |

| Hsieh et al. <sup>14</sup>        | ZnO           | Sputtering | RT         | SiN <sub>x</sub>                                 | PECVD      | 200        | 10 <sup>7</sup>       | 25                             | 4.5                       | -                                                           |

| Kim et al. <sup>15</sup>          | ZnO           | Sputtering | RT         | BZN                                              | Sputtering | RT         | 104                   | 1.13                           | 2.4                       | -                                                           |

| Hsieh et al. 16                   | ZnO           | Sputtering | RT         | Al <sub>2</sub> O <sub>3</sub> /HfO <sub>2</sub> | Sputtering | RT         | 10 <sup>7</sup>       | 8                              | -                         | Post annealing at 265 °C                                    |

| Siddiqui et al. <sup>17</sup>     | ZnO           | PLD        | 350        | BST                                              | PLD        | 500        | 108                   | 2.3                            | 1.2                       | -                                                           |

Table. 2.3. Continued

|                               | Semiconductor |            |       | Insulator                                  |            |       | Electrical properties |                                |                           |                           |

|-------------------------------|---------------|------------|-------|--------------------------------------------|------------|-------|-----------------------|--------------------------------|---------------------------|---------------------------|

| Author                        | Material      | Method     | Temp. | Material                                   | Method     | Temp. | On/Off<br>ratio       | Mobility (cm <sup>2</sup> /Vs) | <i>V<sub>TH</sub></i> (V) | Note                      |

| Lee et al. <sup>18</sup>      | ZnO           | Sputtering | 100   | PVP/CeO <sub>2</sub> /S<br>iO <sub>2</sub> | E-Beam     | 175   | 10 <sup>3</sup>       | 0.48                           | 0.3                       | -                         |

| Carcia et al. 19              | ZnO           | Sputtering | RT    | $Al_2O_3$                                  | ALD        | 200   | 10 <sup>4</sup>       | 17.6                           | 6.0                       | -                         |

| Oh et al. <sup>20</sup>       | ZnO           | Sputtering | RT    | SiO <sub>2</sub>                           | Thermal    | -     | 10 <sup>5</sup>       | 0.1                            | 9.9                       | -                         |

| Chen et al. <sup>21</sup>     | ZnO           | Sputtering | RT    | HfO <sub>2</sub>                           | Sputtering | RT    | 10 <sup>6</sup>       | 1.3                            | 0.3                       | Post annealing at 200 °C  |

| Remashan et al. <sup>22</sup> | ZnO           | Sputtering | 350   | SiNx                                       | PECVD      | 300   | 10 <sup>6</sup>       | 7.8                            | 28.4                      | -                         |

| Cross et al. <sup>23</sup>    | ZnO           | Sputtering | RT    | SiN                                        | CVD        | -     | 10 <sup>5</sup>       | 0.7                            | -                         | Post annealing at 1000 °C |

| Kim et al. <sup>24</sup>      | ZnO           | Sputtering | 100   | SiN <sub>x</sub>                           | PECVD      | 400   | 10 <sup>7</sup>       | 0.29                           | 0.9                       | -                         |

| Chen et al. <sup>25</sup>     | ZnO           | Sputtering | -     | $Al_2O_3$                                  | Sputtering | RT    | 10 <sup>6</sup>       | 27                             | -0.5                      | Post annealing at 400 °C  |

| Lee et al. <sup>26</sup>      | ZnO           | Sputtering | 300   | MgO                                        | Sputtering | 300   | 10 <sup>5</sup>       | 2.3x10 <sup>-2</sup>           | -                         | -                         |

| Ye et al. <sup>27</sup>       | ZnO           | Sputtering | -     | BZN                                        | Sputtering | 500   | 10 <sup>5</sup>       | 0.18                           | 2.2                       | Post annealing at 300 °C  |

| Walker et al. <sup>28</sup>   | ZnO           | Sputtering | RT    | HfO <sub>2</sub>                           | ALD        | 150   | 10 <sup>6</sup>       | -                              | 3.9                       | -                         |

## 2.3 Solution-processed TFTs

Solution-processed ZnO based TFTs can achieve relatively high electrical performance, good visible light transparency, low cost, large areas and mechanical flexibility. Consequently, these devices have attracted considerable attention as the driving elements of active matrix displays instead of Si-based TFTs and organic TFTs. After Ohya et al.<sup>29</sup> first reported ZnO TFTs using solution processing in 2001, many groups began intensive research in this field. However, solution-processed ZnO TFTs have poor performance compared to ZnO TFTs prepared by vacuum or high temperature processing. A combination of additional materials (e.g. dopants) or post-deposition processing are well-known methods to solve these issues. For example, indium zinc oxide (IZO) TFTs have achieved a mobility of 1.8 cm<sup>2</sup>/Vs by using high-pressure annealing (HPA) as a post-deposition process following thermal annealing at 220 °C.<sup>30</sup> Similarly, UV light irradiation<sup>31</sup> and microwave-assisted annealing<sup>32</sup> have been adopted as useful post-deposition processes.

Various passivation layers have also been used to reduce the influence of environmental factors, which can lead to poor device stability.<sup>33-35</sup> The effects of hydrogen exposure on ZnO thin films deposited by sputtering or PLD have also been noted.<sup>36-38</sup> In many instances, this can result in improved device performance. It has been reported that the incorporation of hydrogen in the sputtering gas enhances the carrier mobility. This is thought to result from the elimination of weakly-bound oxygen species, such as -CO<sub>3</sub>, -OH, or adsorbed O<sub>2</sub> on the surface of the films.<sup>39</sup> Hydrogen treatment is already established as an important passivation process for Sibased transistors, where it is used to significantly reduce the density of interface

traps. 40 However, there are limited studies on the effects of hydrogen on solution-processed ZnO thin films and devices.

Boron, aluminium, gallium or indium (elements from group III)<sup>41-43</sup> are commonly used as dopants in ZnO to increase its conductivity. For example, Kwack et al.<sup>44</sup> and Kim et al.<sup>45</sup> have reported solution-processed zinc tin oxide (ZTO) TFTs with carrier mobilities of 4.9 cm<sup>2</sup>/Vs and 6.0 cm<sup>2</sup>/Vs using high temperature annealing processes at 300 °C and 500 °C, respectively. However, doping causes several problems such as the limited availability or high cost (In) of the dopant, lattice deformations between the dopant material and the ZnO or increased complexity of solution formulation. Therefore, undoped ZnO with good electrical properties deposited at low temperature is desirable. Solution processing of undoped ZnO also has the additional advantages of simple and low-cost device fabrication.